If I grab 10 technologists and ask what are the most important issues surrounding the Internet of Things today, one of the popular answers will be “security.” If I then ask them what IoT security means, I probably get 10 different answers. Encryption. Transport protocols. Authentication. Keying. Firewalls. Secure boot. Over-the-air updates. Rogue apps. Data archival. Penetration testing. All the above. Continue reading “Last line of defense for IoT security”

Synopsys Did 90% of Business From Backlog with A Deal Length of 2.5 Years. Err…What Does That Mean?

Here is Trac Pham, Synopsys CFO, from last weeks earnings call:Greater than 90% of Q3 revenue came from beginning of quarter backlog…the weighted average duration of our renewable customer license commitments was about 2.5 years, and we expect duration for the full year to be about 2.7 years.

What does that mean? Why does anyone care that much? Is that good or bad?

Renewable license means that the license is sold for a given period, usually 2 or 3 years, and then it needs to be renewed. Accounting principles (so called GAAP) force this to be recognized quarterly over the period. The whole order is entered into bookings and then every quarter, one twelfth of it (or whatever is appropriate for the term) is moved from bookings to revenue. From the EDA company’s point of view, this makes for a very predictable business. They enter each quarter with eleven twelfths of the term business already on the books waiting to be recognized, so a good or a bad quarter has much less of a yo-yo effect on the bottom line. Which Wall Street likes, since they don’t like surprises.

Perpetual licenses, on the other hand, are the old hardware business model from the days when EDA companies sold not just the software but the hardware on which to run it. The software is sold in perpetuity and a maintenance fee is paid annually or quarterly. Accounting principles force this revenue to be recognized immediately. Ship a $1M perpetual license on the last day of the quarter and that is $1M of revenue that quarter. There are actually other forms of non-renewable license, such as with a given period, but it is complicated enough already.

I think you can see the temptation. If you can switch a $10M license from a renewable license to a perpetual license then you can recognize it immediately. The customer gets a better deal for the same payment terms. It turns out that under those GAAP rules, whether a license is deemed to be recurring or not can swing on just a few words in the license agreement. That is why Wall Street analysts care about the ratios of license types and and why CFOs tell them every quarter. As long as renewable license percentages are not falling, it is good. Deals are not being switched quietly to non-renewable.

The other thing to watch out for is how long the contract lives are. If a company does a $100M deal for a 3 year renewable license, that is a lot less attractive than the same booking for a 4 year period, since in the first case it will drop to revenue at one twelfth per quarter, and in the second at one sixteenth. You can already hear the salesperson: “will you close today if I give you 4 years for the price of 3”.

It is not just Synopsys. Here’s Geoff Ribar, Cadence’s CFO, from last month’s call:We expect weighted average contract life in the range of 2.4 years to 2.6 years, and we expect at least 90% of the revenue for the year to be recurring in nature.

So both Cadence and Synopsys have a contract life of 10-11 quarters. Let’s say 10. If it was all recurring business then 90% should come from backlog with the remaining 10% or so coming from business booked that quarter. Except there are two wrinkles. Revenue recognition is actually done monthly, and in EDA a lot of business is booked in the last month of the quarter. So with a term of 30 months or so, then perhaps only 1/30 of new business will be recognized in the quarter being reported. If all the business were recurring and all new business was booked in the last month, then 29/30s of revenue should come from backlog, or nearly 97%. So there is actually room for a little non-recurring business in there and still clear the 90% threshold.

So the two things that the Wall Street analysts watch out for is recurring license percentage dropping, and the contract lives stretching out. Even if the company is meeting or even exceeding its bookings and revenue numbers, in reality the business is softening and it will show up in future quarters.

Here is the temptation. If a company was going to miss its number by, say, $10M, then they can take one of their $10M orders and make it perpetual. In fact, since perpetual licenses are worth more, the customer might pay even more than $10M, the numbers are even better. Or they can offer to give a customer who was going to place a very large order for a 3 year recurring license a deal for 4 years at only $10M more. In the first case the amount of revenue coming from backlog will decline (in the future), in the second case the contract life will lengthen.

When there was real indiscipline in the industry there were even more games played whereby companies that were already 2 years into a 3 year deal would get an offer to cancel the remaining 2 years and sign up for a new 3 year deal. Or 5. Or 6. At a huge discount, of course, and at the cost of creating a huge hole a few years out. If you sell a company what is essentially software to be used in 2 years’ time, then they won’t be buying any more in 2 years. The company is eating its seed corn. No hunger now, not so good next fall.

A company that does these sort of things to make their numbers is like someone who keeps opening new credit cards to pay the interest on the old ones. It works for a time. but eventually the wheels come off. There is a huge reset, management gets fired, the new management comes in, takes a huge writeoff, and promises never to do such a thing again and hopefully they never do. But when they have a weak quarter, the temptation is always there. Except these days Wall Street understands the model a lot better and so they insist on being told the data every quarter to make sure.

BTW I am not trying to imply that Synopsys, Cadence or anyone else would be playing these games but for the vigilance of Wall Street. I thought it was more interesting to take the actual comments from the most recent conference calls rather than just invent some dry numbers.

Secret Sauce of SmartDV and its CEO’s Vision

SmartDV started as a small setup in Bangalore in 2008 and by now is one of the most respectable VIP (Verification IP) companies in the world. Having a portfolio of 83 VIPs in its kitty and growing, it has a large customer base, including the top semiconductor companies around the world. The company has grown significantly and is raring to grow further. I had an opportunity to talk to Deepak Kumar Tala, Chairman of SmartDV Group of Companies and CEO atSmartDV. This provided further learning about the company’s strengths and philosophies that have played well in pushing the company to newer heights. Deepak also talked about VIP’s future and SmartDV’s vision in future. Here is our conversation –

Q: Deepak, post 2005, the concept of using standard VIPs for SoC verification was picking up. What made you envision the future in this area and become one of the early starters in 2008?

A: The SOCs are becoming complex with every passing month and the time spent on verification is increasing. With rapidly emerging new protocols, companies are finding it difficult to develop new protocol from scratch. Developing a new protocol requires building expertise in a new area. Looking at all these factors, it was clear to me that Verification IPs are going to be used in a big way, and if we could do it right with good quality and right price, we will be successful.

Q: From 2008 until now what were the key factors in transforming the semiconductor industry for such massive usage of VIPs in design verification? What were your company’s stakes and contributions in this transformation?

A: The consumer electronics is changing very fast, so do other sectors. More and more functionalities are being packed in every electronic gadget, creating the need for new protocols’ integration into these products. All companies do not have expertise in all protocols, hence the need for Verification IPs. We have been developing Verification IPs for all emerging technologies and have helped big companies in bringing up newer products in the market, faster. If you look at our portfolio of VIPs, we have covered almost all the protocols.

Q: Your internal language and compiler technology for developing VIPs is very effective and performance optimized. Was it a conscious choice to develop it first before VIP development or you learnt it while developing VIPs? Can you provide some specifics about it? Going forward, do you plan to add more optimizations in this technology?

A: We built the compiler technology as soon as we started our company; it took a few iterations before we stabilized the compiler. After stabilizing the compiler, we started building Verification IPs. With every major revision of the compile technology, we improved performance and also moved higher to reduce the amount of code to be written manually. From the very beginning we knew that developing a Verification IP manually can be an uphill task. So having compiler technology to automate the writing of VIPs was the key for aligning with our business strategy and gaining competitive advantage.

We have made a few major changes in our LRM and compiler so that we can move code from a VIP to an Emulator. Also with some little modifications, we can move the same code base for post silicon validation using FPGAs. These are some of the major enhancements happening in our compiler, right now.

Q: One of the key differentiating factors in your VIP offering is the delivery of a smart testbench with a comprehensive test suite with each VIP. Can you provide some specifics about how this provides higher efficiency and productivity in the customer environment?

A: Traditionally Verification IPs use BFM for generating traffic and checking protocols. The users have to write all testcases and functional coverage models. This was fine in good old days when sufficiently long time-to-market was available. But now the time-to-market window is very short, the requirement has shifted significantly; the users need to jump start their verification. The only way to enable the user to jump start the verification is by supplying a complete test solution along with each VIP. With our VIPs, we provide complete testsuite for each and every protocol, functional coverage models, testbench examples to allow testing of each and every feature, and very high quality documentation.

Q: How about the automated development of verification environment and testcases which incurs minimum cost in VIP development? Can you provide some details about this automation?

A: We have developed a language which is suited for writing verification environment and Verification IPs. BY using this language, we can write the code with higher level of abstraction and reuse. Due to this we are able to write the verification environment and testcases very fast.

Q: What enables you deliver a VIP for a new protocol in the shortest time after its release?

A: We can complete about 85% of a new protocol in a very short time due to our compiler technology and strong processes in place. As soon as we get a new specification in hand, we have a team of engineers who extract the features from the specification and create a testplan, the functional coverage requirements, and then finally break down the specification into blocks for which the code has to be developed. By using our compiler technology, we automate the development of code for each block. In a short duration of about a few days to a week, we normally can create a framework of a VIP up and running.

Q: In which direction do you see the VIP market heading in the near future? How would be the segmentation between commodity and premium?

A: As the complexities of SOCs increase, there is going to be more and more demand for complete VIPs. Also, engineering help from VIP companies for deployment of these VIPs will be needed. In such a scenario, a commodity type of model will be of no help to customers. A premium model where a VIP is delivered as a complete solution along with the engineering resources to help deployment and coverage closure will be desirable.

Q: How has been the business after opening of SmartDV’s new office in San Diego last year? What are the plans for expanding in other regions?

A: We have been maintaining a low profile, as we have been focusing in building quality VIPs and improving our compiler technology. Last year we felt the need of expanding our customer reach, so we started our new office in USA. With the new office in operation and close proximity with customers, we have been able to expand our reach within our existing customers and also find new customers. It was a key strategic decision to create awareness about SmartDV products & services, not only in North America but also in the worldwide semiconductor market. We have been able to communicate to our customers about our seriousness in VIP business and long term relationships with them. We will be further expanding our operations in Japan, Russia, South Korea, and Taiwan.

Q: What is your future vision about SmartDV into VIPs? Do you see another level of transformation in this area; for example customization against standardization?

A: We have been doing custom protocols for some time now; we also customize our existing VIPs to meet the needs of our specific customers. Due to our compiler technology, we can generate code which is specific to a specific customer. Most of the big companies have customization to standard protocols to get better performance or to suite their product needs.

Q: Do you envision any other area of focus in VIP or IP as such for your company?

A: We are getting into Simulation Acceleration, which is going to be the next level for simulation VIP. We are committed to deliver all our VIPs in SimXL platforms.

This was a very enriching conversation with Deepak. I see that the company has created a solid foundation in VIPs and is continuously improving to cover the verification space including emulation and post silicon validation through its innovative compiler technology. The company’s continued focus on providing complete VIP solutions, efficiently and faster, will go a long way in its future success.

Pawan Kumar Fangaria

Founder & President at www.fangarias.com

GaN Technology — Contributing to Medicine in No Small Way

In past posts, the disruptive nature of gallium nitride (#GaN) semiconductor technology, especially eGaN® FETs, was discussed…now with significantly higher performance at an equivalent cost, the inevitability of GaN displacing the aging power MOSFET is becoming clearer.

This post highlights a specific end-use application that affects all of us – the contribution that #GaN technology is making in medical applications with enhanced patient mobility using wirelessly powered devices and improved diagnostics with higher resolution equipment.

Medical Applications: Introduction and Overview

Being untethered to the power cord not only makes life easier for patients and health workers, but also increases safety and allows health care to be administered faster and more efficiently. Imagine medical teams never having to plug in a power cart while rushing to save a life in an emergency room or having to worry about the tangle of wires that can interfere with the delivery of IV fluids.

From a patient’s point of view, think about eliminating the need to have infection-prone wires extending from the body to recharge the batteries for a heart pump. And, in the world of diagnostic procedures, just think about the impact of significantly increasing the resolution of scanning equipment such as sonograms and MRI, or the ability to swallow a miniaturized X-Ray machine embedded in a pill to perform a colonoscopy.

These improvements to the world of medicine are being enabled by gallium nitride technology. Let’s take a closer look.

At the Hospital – Untethered Emergency Carts, Unplugged Bedside Monitoring Instruments, and Untethered Patients

We are all familiar with the chaotic environment in which emergency medical personnel navigate at life-saving speed and can thus appreciate the advantage of having the equipment readily available without the need to “find power outlets” .

Even at a patient’s bedside, not having power cords will be welcomed – for ease of moving instruments, avoiding accidental unplugging of critical equipment, reducing the risk of electrical shock, and reducing the potential to breed bacteria. The emerging availability of wireless power transfer is making wireless medical carts and bedside stands a reality.

The advancement of wireless power transfer is an electronics industry-wide movement. Industry leaders including Hewlett Packard, Intel, Texas Instruments, Samsung, and Witricity have established a consortium (A4WP) for consumer and computing equipment. This technology is applicable to hospital environments, which is using frequencies at both 6.78 and 13.56 MHz. In addition to the convenience, wireless power will increase safety and reduce price by removing cable clutter around the patient.

On the Patient – Heart Pumps, Pacemakers, Muscle and Nerve Stimulators, and Electric Wheelchair Recharging

In addition to untethering the instrument carts in the emergency room, having #wirelesspower available enables patients to be more comfortable while bedridden and increases their freedom of movement when ambulatory.Likewise, if a patient is bound to an electric wheelchair, the need to recharge batteries can be accomplished with a “drive over” mat that will charge the battery without the need to plug in. As with electric vehicles, electric wheelchairs can recharge simply by rolling over a wirelessly coupled mat. This vehicle recharging technology is in operation today with drive-over chargers for electric cars and buses.

There are also numerous direct patient applications for wireless power transfer enabled by GaN technology. The figure at the top of this post illustrates some of the high-impact applications under development and in clinical trials. These applications involve heart pumps and nerve stimulators that do not require wires – wires that are prone to infection – protrude from the body in order to “plug in” for power. Wireless charging is not only more convenient, it is safer for the patient.

Diagnostics – MRI, Colonoscopy

Resolution is a critical attribute of all medical scanning devices, such as sonograms, CAT scans, and MRI imaging. Equipment manufacturers are very excited about using eGaN® FETs to increase the speed and precision with which they can conduct scanning measurements. In the case of MRI systems, eGaN® FETs are used in the transmit functions, which require extremely high RF power for both the power supply and power amplifier being constrained by heat. The small size and efficiency of eGaN® FETs allow the transmit function to be placed closer to the patient allowing effective higher power capability for faster imaging. This faster imaging can be taken as either more image slices in the same time for higher resolution, or shorter scan time for more efficient equipment usage.

The receive coils are placed in direct contact with the patient and are limited by heat. Replacing silicon-based components with eGaN® FETs to detune these coils for the transmit phase and tune them for the receive phase yields a drastic reduction in power dissipation, allowing a higher density receive matrix. This provides more information in the same space for higher resolution images. Thus, medical professionals will have more accurate images and a patient’s care will benefit with improved diagnosis.

Perhaps the most innovative medical application enabled by the extremely small size of the eGaN® FETs is the “colonoscopy pill”. This pill contains a miniature X-ray machine that, after ingestion (no pre-purging needed!), creates a 3-D image of the intestinal track as it passes through the patient’s digestive system.

The scanned images are transmitted wirelessly to a receiving unit placed on the patient. Once the pill has passed through the patient’s system, physicians can analyze the digital information stored on the receiving unit. Imagine, no more discomforting overnight preparation for the traditional colonoscopy! This “pill” and procedure is the result of EPC’s customer Check Cap, and is currently undergoing European agency trials and is on track for final evaluation by 2016.

In no small way, eGaN® FETs are contributing to changing the cost curve of medicine.

Summary: GaN Technology for Medical Applications

The world of semiconductors is undergoing a technological disruption and medical applications that take advantage of high performance eGaN® power transistors and integrated circuits are emerging rapidly. In this post, applications improving the quality of medical care were presented:

- Untethering the all-important “medical cart” containing emergency instruments to make movement of the cart less of a contributor to bacterial infestations, as well as faster and easier to address patients.

- Removal of the necessity to have infection-prone “wires” protruding from a patient’s body because they are needed to power heart pumps, or nerve stimulators.

- Increase in the resolution of body scanning devices, such as MRI equipment, giving more accurate information about the condition of patients at a lower cost.

- Introduction of new diagnostic procedures, such as the “colonoscopy pill,” giving doctors more precise critical information, while easing medical procedures for the patient and reducing costs.

#GaN technology is contributing to significant improvements in medicine. Taking an even broader view, gallium nitride is displacing silicon as the fundamental material used for power conversion with the promise to displace silicon not just in power transistors, but in analog and digital integrated circuits as well. EPC is pursuing this $350B semiconductor market, and the reason is simple, #GaN technology is faster, smaller and, now, price competitive with MOSFETs…

Why wouldn’t this huge market be worth attacking with this disruptive technology?

Also read:

GaN Technology for the Connected Car

Four Things a New Semiconductor Technology Must Have to be Disruptive

FD-SOI: GlobalFoundries 22nm Update

As I said yesterday, last week was the GSA Analog/Mixed-Signal working group completely dedicated to FD-SOI. ST went first and had a presentation that was a mixture of an introduction to FD-SOI that I have covered times that are too numerous to mention. Then they did a dive into analog and RF capabilities for FD-SOI that went very deep into two test projects, deeper than I could follow in detail (my PhD is in software not RF design). But the key is in the picture above. The pictures on the right show how back-biasing is actually applied. You apply a positive voltage to the back of the N transistors and a negative one to the back of the P. The graph on the left shows the result. The tiny red line shows how substrate bias works in a bulk process: you can only do a little and it isn’t very effective. The blue line is what you can get with FD-SOI biasing. Actually, since biasing can go to 3V I believe you can do even more. See also FD-SOI: Samsung Opens the Kimono a Little Last up was Jamie Schaeffer of GlobalFoundries. Their introductory slides on the motivation for FD-SOI were largely the same as ST and Samsung. But GF’s process is 22nm, what they call 22FDX. They had 3 reasons for doing 22nm rather than 28nm:

- they have a big fab in Dresden that can do 22nm but can’t go to 14nm

- 22nm doesn’t require double patterning (it is no coincidence that Intel’s first FinFET process was also 22nm)

- they can address a bigger market with 22nm than 28nm

They actually have several flavors of the process, to address slightly different markets at the cost of a couple of extra mask steps in most cases. See above for details but the 4 process options are:

- ulp: ultra-low power

- ull: ulra-low leakage

- uhp: ultra-high performance

- rfa: integrated RF and analog

The 22FDX body biasing works the same as in 28nm (only more so). With FBB they can get low voltage operation down to 0.4V which is the lowest of any process in existence or that GF knows to be in development. With RBB they can get leakage down to 1pA/um. Those are both impressive numbers. There are also all the advantages in terms of being able to tune gain, linearity, noise immunity and more in analog/RF designs. There are also multiple transistor types which allow you, as you would expect, to get different power/performance points. With FBB and RBB each of these transistors can hit multiple points. See the above diagram for more details. These transistors can all be mixed on the same die. So for an IoT device you can imagine having a little watchdog processor waiting for something to happen: a button press, a timer expires, motion is detected. This can use RBB for the lowest possible leakage. The assumption is that the watchdog does not need much performance, although that can depend on the activity obviously. That can then wake up the comms processor that has integrated RF. Finally a power hungry image processor is awoken using FBB and fast transistors to analyze the scene and zoom on on the area of interest. Then everyone goes back to sleep except the watchdog. The bias gives you a lot of flexibility. There is nothing there yet, but some version of Jamie’s presentation should appear next week on the GSA working groups archive page here. UPDATE: it is now up

A Security Idea for EDA / Embedded Design

I’m on a mission to find novel ideas for EDA / embedded design tools. One I have been discussing on and off with a DARPA friend for at least a couple of years is how to grade the security of a hardware design or, more comprehensively, the security of an embedded system including hardware and the software running on the hardware.

This feels like something that would be useful to do. After all, in hardware we can grade testability, in hardware and software we can grade test coverage and in ISO26262 there is at least a subjective concept of grading safety risk. Wouldn’t it be nice to know that embedded systems in missiles, personal payment systems, automobiles and medical implants had a similarly objective level of security? Of course these systems have well-defined defenses against known exploits, but intuitively a security metric should not be determined just by defenses against the problems you know but also by also by some measure of security risk in the problems you don’t know.

Security metrics are not very well-developed even in the software space, but there are interesting papers that could be used as a starting point for an embedded security metric. Manadhata and Wing at CMU developed an attack-surface metric for software which considers a static measure of total vulnerability of a system where the attack surface measures through how many directions weaknesses in the system could be attacked. This can be elaborated in several directions, particularly to use “Common Weaknesses and Exposures” documented by the Mitre Corporation as the basic weaknesses around which you build a metric based on accessibility, privilege and so on. An example weakness would be the well-known buffer-overflow problem.

What is appealing about a generalized version of the approach, aside from delivering a metric, is that it depends on a quite finite set of well-known weaknesses (~200 in the Mitre list). Contrast this with the very wide range of possible attack types. What we know about security today focuses almost exclusively on preventing specific classes of attack (stealing a PIN by somehow getting secure access for example) but the total class of possible attacks is almost unbounded. The approach suggested here uses the fact that each attack starts by exploiting one of a relatively small set of weaknesses and is not concerned with the objective or mechanics of the attack.

So to build a metric for the security of an embedded system, we first need a list of Common Weaknesses and Exposures. The Mitre list is a good starting point, and presumably could be enhanced by a list of common weaknesses in hardware. What these should be will require some debate but may not be as difficult as it sounds. Especially worthy of consideration are weaknesses which can enable denial of service or reduction in quality of service; it is often easier to see how these could be accomplished than to see how data could be maliciously injected or stolen from the system. Could you force bridge FIFOs to overflow? Is there a way to cause a cache to repeatedly flush? Can a state-machine be pushed into a deadlock state? Can a privilege be raised on a data transfer from a non-privileged interface IP?

You might argue that if a tool could detect these problems, you would fix them anyway. The same should be true for common software weaknesses and yet they continue to be at the root of almost all software attacks. Apparently the fact that a problem can be detected does not always guarantee it will be corrected. Sometimes this happens through oversight, sometimes because the cost of a fix exceeds the (perceived) value of the fix. But what is an acceptable compromise in one context may not be acceptable in another. A security metric as sketched here would be a way for a prospective customer to assess if an embedded design really meets their security expectations.

Stay tuned for more ideas…

Test Driving Analog/Mixed Signal Design for the Internet of Things

The Internet of Things (IoT) is creating urgent demand for a new generation of analog/mixed-signal (AMS) designs, some of which also contain MEMs. To efficiently create the myriad of AMS devices at the edge of the IoT requires a design environment that is affordable and easy to use, but powerful enough to create the widely diverse range of products needed for deployment in the IoT.

Though most of these devices will be inexpensive, there will lots of them – millions and soon billions of form-factors of every description, all created and deployed to gather analog information in the physical world. Wearables may be the media darlings at the moment but in fact examples range from traffic monitoring, smart meters and video surveillance for smart cities, to medical devices that monitor glucose levels, heart rates and mobility and everything in between. And don’t worry, chip designers. These devices will generate a tsunami of analog data that must be digitized and transmitted either to the desktop or to data centers for analysis on phablets, laptops, PCs and servers and systems – all of which contain the more expensive, higher-margin silicon that remains the bread and butter for our industry.

If you’re an AMS designer, you know all about the challenge that comes with creating mostly analog circuitry along with some digital—the so-called ‘Big A/little D’ designs that also can include MEMs functionality. A new generation of affordable, easy-to-use AMS design tools from Mentor Graphics called Tanner AMS IC Design flow is emerging that directly address these challenges, providing a complete flow tailored for the big-A/little-D AMS market for every stage of the design process as well as MEMs. These tools deliver myriad benefits, including increased automation, improved accuracy, lower NRE costs and reduced time to market.

It’s always a tough decision, however, when evaluating and adopting a new set of design tools and capabilities, especially for AMS design. That is why Mentor Graphics has created the Tanner AMS Virtual Lab. Now you can test drive Tanner tools online and experience firsthand how intuitively easy it is to use this powerful, fully integrated and cost-effective AMS design flow. The Virtual Lab covers all aspects of AMS design: schematic capture; mixed-signal simulation or co-simulation; digital synthesis with DFT support; analog place and route; and high-speed, “sign-off ready” timing analysis for tape-out along with MEMs design and layout.

All it takes to access the virtual lab environment is an updated Web browser. There’s no downloading, so no IT department approval is required. Sign up and access to the lab is available for 30 days.

FD-SOI: Samsung Opens the Kimono a Little

Last week there was a meeting of the GSA Analog/Mixed-Signal (AMS) working group. It was completely focused on FD-SOI (I hate that name, especially since FinFET is also fully-depleted. I vote for BoxFETs.) It was a bases loaded meeting with presentations from ST Microelectronics (calling in from France close to midnight), Samsung and GlobalFoundries. That is 3 for 3 of companies that have announced FD-SOI manufacturing.

Here’s the situation. ST got FD-SOI to the commercial manufacturing stage at 28nm. Others, notably IBM, did research in the area (IBM uses partially depleted SOI for its high-end servers, now manufactured by GlobalFoundries, which acquired IBM’s semiconductor business). Samsung announced that they were licensing ST’s process. However, until yesterday, I had not heard much about what the true status was. Then GlobalFoundries announced a 22nm FD-SOI process (actually a family of processes that they market as FDX). The motivation for 22nm was that they wanted a process that was more competitive with 14/16nm FinFET and they wanted to get maximum use out of the existing installed equipment in their Dresden fab. In another wrinkle nothing to do with FD-SOI, GlobalFoundries also licensed Samsung’s 14nm FinFET process.

So the current score is (I added TSMC for completeness):

[TABLE] class=”cms_table_grid” style=”width: 400px”

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” style=”text-align: center” | Foundry

| class=”cms_table_grid_td” style=”text-align: center” | FD-SOI

| class=”cms_table_grid_td” style=”text-align: center” | FinFET

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | STMicroelectronics

| class=”cms_table_grid_td” | 28nm

| class=”cms_table_grid_td” |

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Samsung

| class=”cms_table_grid_td” | 28nm from ST

| class=”cms_table_grid_td” | 14nm

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | GlobalFoundries

| class=”cms_table_grid_td” | 22nm

| class=”cms_table_grid_td” | 14nm from Samsung

|-

| class=”cms_table_grid_td” | TSMC

| class=”cms_table_grid_td” |

| class=”cms_table_grid_td” | 16nm

|-

So on to what Kelvin Low from Samsung said. The main motivation for them to license FD-SOI is that the #1 concern of most customers, and the fastest growing part of the market, is lowest cost per transistor followed closely by low power. People were also concerned with having multiple sources, which had been a problem for ST that Samsung, with its massive manufacturing resources, could help solve. FinFET has a place, obviously, for the leading edge but it delivers high performance but at increased cost, which is the wrong tradeoff for many. FD-SOI involves fewer masks than bulk and about half as many as FinFET (in the front end, the metal stack BEOL is unaffected). Also, the back biasing of FD-SOI is really important. FBB (forward) allows really low voltage operation and RBB (reverse) allows very low leakage standby idle modes. Perfect IoT fodder.

Since this was a mixed-signal working group, Kelvin went into some of the advantages of FD-SOI in the analog RF world. The big advantage of FD-SOI is to be able to use the back-biasing not just to decrease power but add dynamic trimming, gain controlled amplifiers and high gain. Andreia Cathelin of ST had also covered this in her presentation at a level of detail that overwhelmed most of us in the room (certainly me). But the results she had of papers that ST had presented at ISSCC (which I did understand) were undoubtedly impressive. They could do things with FD-SOI that are impossible with bulk (and I think pretty much impossible with FinFET but that is beyond my pay grade).

One thing that I hadn’t realized is that you can run a hybrid process with bulk on some parts of the die (using one extra mask to remove the box) to be able to add ESD structures, BiCMOS options and more. Photomicrograph above.

The current status at Samsung is that wafer level qualification was completed in 2014 and product level reliability in March of this year. PDKs are available. Multiple MPW shuttles are planned (see the graph above for details). The process is currently in its initial ramp, but the base 28nm process of which FD-SOI is a sort of derivative, has alreay run over 2M wafers. The BEOL is completely the same and the FEOL is simpler but still uses the same gate-first HKMG structure.

So what of the future? Things Samsung were not ready to announced (yes, we asked) was what their future process roadmap for FD-SOI would be (22nm, 14nm?). They currently have SRAM, ROM, OTP but are not ready to announce any non-volatile memory option. But you can see some of the directions from the above, Kelvin’s final slide.

There is nothing there yet, but some version of Kelvin’s presentation should appear next week on the GSA working groups archive page here.

And trivia fact of the day. Kimonos are Japanese, as you probably knew. The equivalent in Korea is called a Hanbok.

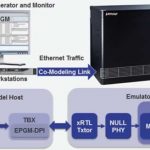

Testing Ethernet with virtual co-modeling

Ethernet is suddenly a hot topic in SoC design again. The biggest news may be this: it’s not just the cloud and enterprise networks. Those are still important applications. The cloud is driving hard for more ports at 25G server and 100G switch speeds according to a recent Dell’Oro Group report. Enterprise networks are driving for more ports at what are becoming intermediate speeds, with Cisco advocating 2.5G and 5G to support existing Cat5 and Cat6 cable. Continue reading “Testing Ethernet with virtual co-modeling”

NIWeek: Xilinx Inside

Being from Britain, NI always means Northern Ireland when I see it. After all the official name of my country is the United Kingdom of Great Britain and Northern Ireland, giving us the same problem as the United States of America, the full name is a mouthful. So we abbreviate the country to UK and call ourselves British or even Brits. But it also stands for National Instruments and every year they have an week-long conference known as NIWeek.

National Instruments are mostly on my radar for a design environment that they have called LabVIEW. As it says on their website:If you can turn it on, drive it or fly it, chances are NI and LabVIEW made it happen.

The product has been around for over 20 years and provides a graphical interface for hooking up everything in the lab and driving the measurement process.

What is NIWeek? The 21st annual NIWeek conference began August 3 in Austin, Texas (where DAC will be for the next two years, by the way), and once again brought together the brightest minds in engineering and science. More than 3,200 innovators representing a wide spectrum of industries, from automotive and telecommunications to robotics and energy, discovered the latest technology to accelerate productivity for software-defined systems in test, measurement, and control.

Most systems in test, measurement and control ship in relatively low volumes, sometimes astoundingly so. When I was doing my PhD I visited HP (presumably now that group will be Agilent if it still exists) and one thing they built was huge analyzers for satellite downlinks. I forget how many they expected to sell but I was surprised how low a number it was (and how much one cost). But back then how many people needed to analyze satellite signals. I bet they sell a lot more with DirectTV, Sky, GPS and more. Low volumes and a reasonable power budget (these are typically not tiny hand-held devices) make it a perfect application for programmable fabrics made by Xilinx, what you probably casually call an FPGA but by the time there are multi-core processors and whole peripheral fabrics, the name is starting to get obsolete. But I suspect Xilinx is fighting a losing battle in trying to get away from it. Like the Association of Computing Machinery just embrace the weirdness of calling your iPhone and its software a machine. It worked for IBM.

Xilinx also has a broad portfolio of different device families at different performance points (and price points). Here is a summary showing the huge range of applications. My favorite, the Phasor Measurement Unit. “Scottie, get that Zynq SoC fired up quickly, the shields are failing.”

[TABLE] class=”cms_table_grid” style=”width: 593px”

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | ARTSENS

| class=”cms_table_grid_td” | Use Ultrasound to determ ine hardening of arteries for potential

flag of heart disease.

| class=”cms_table_grid_td” | Zynq 7020 SOM

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Airbus tools

| class=”cms_table_grid_td” | Three smart tool families that perform different manufacturing

processes: drilling, measuring, and quality data logging and

tightening – Zynq sbRIO is foundation of these families.

| class=”cms_table_grid_td” | Zynq – sbRIO SOM

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Samsung

| class=”cms_table_grid_td” | Samsung’s 3D beamforming algorithms and multi-user interface

brought all four emulated handsets online and immediately

bumped the 5G data thouroughput above 25Mbps per user

as compared to 2Mbps per user without 3D beamforming .

| class=”cms_table_grid_td” | Virtex-7 FPGA

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Nokia Networks

| class=”cms_table_grid_td” | Prototype mmWave system that transmits 10Gps @ 73 GHz over 200m.

| class=”cms_table_grid_td” | Kintex-7 410T FPGA

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | FireFly ProSlab 155

| class=”cms_table_grid_td” | A mobile, Diesel-powered turf cutter/slab harvester called the FireFly ProSlab 155 that harvests, stacks, and palletizes turf slabs 20% faster than competing machines while consuming only half the fuel.

| class=”cms_table_grid_td” | Zynq SoC

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Model cRIO-9039

| class=”cms_table_grid_td” | The NI CompactRIO controller pairs a 1.91GHz, quad-core Intel Atom CPU with a Xilinx Kintex-7 325T FPGA—the highest-performance CompactRIO ever released.

| class=”cms_table_grid_td” | Kintex-7 325T FPGA

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Phasor Measurement

Unit (PMU)

| class=”cms_table_grid_td” | (Used in condition monitoring test beds, shown at NI Week 2015)

| class=”cms_table_grid_td” | Zync SoC

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | eCall

| class=”cms_table_grid_td” | The in-vehicle eCall device automatically dials 112 in the event ofa serious road accident, and wirelessly sends airbag deployment, impact sensor information, and GPS coordinates to local emergency agencies.

| class=”cms_table_grid_td” | Virtex-6 FPGA

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Fujitsu

| class=”cms_table_grid_td” | Remote radio head testing.

| class=”cms_table_grid_td” | Virtex-6 FPGA,

Kintex-7 FPGA

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Hyundai Exoskeleton

| class=”cms_table_grid_td” | Exoskeleton that senses a users physical intent to move; actuators and sensors help people that cannot walk the ability to do so.

| class=”cms_table_grid_td” | Spartan-6 LX150 FPGA,

Kintex-7 160T FPGA

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | IMSat/DSL

| class=”cms_table_grid_td” | IMSaT’s Cavitation Research Group working in conjunction with Diagnostic Sonar Ltd. (DSL) wants to create a new therapy that uses focused cavitation to disrupt cancer tissues, making them far more susceptible to cancer-killing drugs.

| class=”cms_table_grid_td” | Xilinx Virtex-5 SX95T

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Passive, Wi-Fi radar

| class=”cms_table_grid_td” | uses the ambient Wi-Fi RF already injected into the air from existing Wi-Fi access points. Therefore, the use of this equipment is essentially undetectable, which has extremely interesting implications for military and security surveillance applications, as illustrated by this image:

| class=”cms_table_grid_td” | Spartan 6

|-

There is more detail on most of these applications on Steve Leibson’s Xcell Daily Blog here.