Wi-Fi has this reputation as being a power hog. It takes a relatively big processor to run at full throughput. It is always transmitting all over the place, and it isn’t very efficient at doing it. Most of those preconceived notions arose from older chips targeting the primary use case for Wi-Fi in enterprise and residential environments. There is a wall-powered, always-on access point for high performance clients like PCs and smartphones to connect with, streaming data faster and faster.

Those Wi-Fi SoCs were optimized for performance, not power. The pervasiveness and ease of IP connectivity drove many companies to try to reduce Wi-Fi power and footprint to make it more compatible with embedded devices, and more recently, maker modules and IoT devices. Some have been more successful than others – particularly Atmel, Electric Imp, GainSpan, Microchip (from the ZeroG acquisition), Redpine Signals, Silicon Labs, and TI come to mind.

There is a new specification in development called IEEE 802.11ah. It changes frequencies from the 2.4 or 5GHz bands into the sub-GHz band, giving it better range and an improved link budget. Several power-saving mechanisms are being considered, such as Target Wake Time which allows napping until a transmit slot arrives. Proponents of other wireless sensor network technology rained all over the idea, saying competing specifications already deliver the same benefits without all the hassle.

However, none of the companies we’ve mentioned so far are Qualcomm.

One of the more fascinating aspects of our research for Chapter 9 of our upcoming SemiWiki book on mobile has been just how much resistance Qualcomm got from industry naysayers in the early days of CDMA. It was said to “violate the laws of physics”, and it could never be shrunk into a mobile handset, and it wouldn’t work reliably under real-world signaling and loading. Fortunately, there were a few supporters like William C. Y. Lee who understood how powerful digital encoding technology and the Viterbi decoder were. We see how that turned out, though it did take a few years and a detour to another processor after the first six million chips.

Klein Gilhousen of Qualcomm said a few years back, “We have always recognized that the key to feasibility of CDMA was VERY aggressive custom chip design.” We have been saying for some time here at SemiWiki that we are waiting for SoCs specifically designed for IoT tasks to appear. If there is a company that can pull off low-power Wi-Fi designs, it’s Qualcomm – just substitute “IoE” (the term Qualcomm prefers) for “CDMA” in Gilhousen’s statement.

We are seeing what the Atheros acquisition does for Qualcomm. In a world where mobile growth rates are settling down and IoT is the next field of opportunity, Qualcomm has chips for low-power Wi-Fi. Note these designs are not for 802.11ah as of yet – Qualcomm is a sponsor of the spec, but it is still in early development.

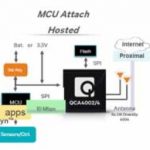

Rather, Qualcomm has taken experience from the CDMA portfolio and added new ideas for Wi-Fi in existing 2.4/5GHz settings, including its AllJoyn thin client software. For example, let’s look at the QCA4004, implementing 802.11n 1×1 SB/DB low power Wi-Fi. It is flexible enough for three Wi-Fi use cases:

The first is the traditional one, a peripheral to a host. The second is the embedded case, with a local MCU. The third is the IoE case where the onboard core is powerful enough to run AllJoyn.

Atheros first licensed the Tensilica Xtensa core back in 2005, way before Cadence acquired Tensilica in 2013. The QCA4004 was introduced almost two years ago, and its press release and datasheet have no details on the processor core inside. A more recent Qualcomm presentation at IoE Day 2014 in Shenzhen reveals a Cadence Xtensa core at the center of the QCA4004, running at 130MHz with the ThreadX RTOS from Express Logic. That allows the same software architecture to be used whether an external MCU is present or not, including a dual IPv4/IPv6 stack (take that, TI) and AllJoyn API.

The Qualcomm influence is more evident in two areas of the QCA4004 design. The first is the antenna diversity feature, with an RSSI algorithm in hardwired DSP logic to determine which antenna gives the best results. The second is a Green Tx feature, allowing the Tx power to be reduced to the lowest acceptable level for a given throughput. The active power figures for the QCA4004 are worth noting. At 2.4GHz, Tx power at 18dBm is 230mA, while Rx power is 60mA. Sleep mode gets down to 130uA.

The core choice of Cadence Xtensa puts Qualcomm in new territory for smaller, cheaper, more configurable chips for low-power Wi-Fi. Naysayers beware. While other solutions might have traction in industrial IoT environments, the combination of Wi-Fi ubiquity, the right chip design expertise, AllJoyn software, and an ecosystem that includes Microsoft makes Qualcomm a strong player in consumer IoT use.

We’re tracking what else Qualcomm is up to as they remake the company.