Breker Verification Systems solves challenges across the functional verification process for large, complex semiconductors. This includes streamlining UVM-based testbenches for IP verification, synchronizing software and hardware tests for large system-on-chips (SoCs), and simplifying test sets for hardware emulation and post-fabricated silicon. The Breker solutions are designed to layer into existing environments.

Adnan Hamid is founder CEO of Breker Verification Systems and the inventor of its core technology. Under his leadership, Breker has come to be a market leader in functional verification technologies. Prior to Breker, he managed AMD’s System Logic Division, and also led its verification team to create the first test case generator providing 100% coverage for an x86-class microprocessor. In addition, Hamid spent several years at Cadence Design Systems and served as the subject matter expert in system-level verification, developing solutions for Texas Instruments, Siemens/Infineon, Motorola/Freescale, and General Motors. He holds 12 patents in test case generation and synthesis. He received Bachelor of Science degrees in Electrical Engineering and Computer Science from Princeton University, and an MBA from the University of Texas at Austin.

What is your background?

I knew at a young age that I wanted to be in the business of building computers. While studying Electrical Engineering and Computer Science at Princeton University, I worked an on-campus job in artificial intelligence at the psych lab. It opened a whole new world of innovation for me and convinced me that wherever possible, we must teach computers to do our work for us. I stumbled upon functional verification early in my career and led a team at AMD responsible for verifying that the AMD x86 chips were functionally correct. Given our time pressures, I invented an AI problem solver-based test generator, which was a huge success for our stellar team in meeting our deadlines and providing 100% coverage. I moved on to verification methodology and system-level jobs and understood I could envision a better solution to the disparate nature of verification across the full system flow.

What made you start Breker?

“When there’s a gold rush, sell pick-axes” was sage advice shared by my investment manager. This, coupled with the increasing costs in verification and my career success, encouraged me to take the risk to start Breker that pioneered a graph-based approach to automation of C-test generation across different platforms. This represents a big improvement in verification, and was an opportunity I simply could not ignore.

Where did the name “Breker” come from?

On my first day of my Executive MBA at UT-Austin, we were asked to share a blurb about who we were and what we do. Never known to do the expected, when it was my turn, I said, “I break things for a living.” It livened up a class of middle-management folks, and earned me the nickname of “The Breaker.”

Toward the end of my course, my team participated in a business case competition and pitched my idea for a system-level verification product. When searching for a name for the project, we decided on Breker, which sounded bold while capturing what we do: break things.

You and your wife founded Breker. Is she involved? What about Breker’s executives and board members?

My wife is a fellow MBA and built her career in investment banking. She co-founded Breker with me and has been a part of this journey from the beginning, where we complement each other’s strengths across the functional areas required to build a thriving business. She serves as Chief Financial Officer.

We have a fantastic, motivated team at Breker who are all excellent at what they do. Industry veterans with some of the most creative minds in the space of verification have naturally gravitated toward Breker, which pioneered the field of Portable Stimulus. Seasoned board members like Jim Hogan and Michel Courtoy believe in the vision for Portable Stimulus and see the far-reaching benefits it can bring to users.

How long ago was Breker founded? Where is its corporate headquarters located? How many employees does Breker have?

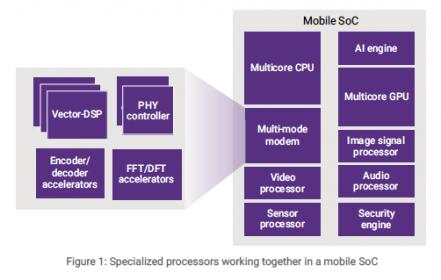

Breker was founded in 2003 and we started selling portable stimulus solutions a few years later. Since then, our product portfolio has grown significantly. It now includes test suite synthesis flows whose output is optimized for universal verification methodology (UVM) block verification, Software-Driven Verification (SDV) and Post-Silicon environments, providing a complete verification solution that generates stimulus, checks and coverage. Privately funded and headquartered in San Jose, Calif., Breker has global presence and a core team of 25 people.

What is the Breker vision and how are you going to change verification?

Since the beginning of HDL-based verification more than 30- years ago, the industry has dreamed of “specification-driven verification” where the original product specification is used to drive the entire verification process. Breker is the first company that truly realized this vision and, now that Portable Stimulus is an Accellera standard, the industry is accepting this notion. Starting with an easily understood spec and automating the entire process for stimulus, checks, coverage and debug for the most complex verification problems is the path Breker is on.

What keeps your users up at night?

Verification is absolutely at the sharp end of semiconductor development. It continues to take 70% of the overall process, and represents the most risk if it goes wrong. Verification managers are most worried about a bug escaping from this process into the final chip, causing a re-spin with the associated schedule slip and cost. To avoid this, they drive as comprehensive a process as possible, with high coverage and quality testing. They are always time and resource limited. It is always interesting, though, that if they are able to save some time, they will put that back into extra testing rather than shrinking the schedule.

What do your top users find so useful about Breker and your Trek portfolio?

Given the complete solution focus, there are two areas of interest. The first is what can PSS do for their individual flows. Depending on their area of interest, they enjoy eliminating the more painful activities around UVM test authoring and tracking corner-cases. Also, complex activities in a Software Driven Verification (SDV) flow, often on an emulator or post silicon validation where they use their verification test suite for the first time while gaining visibility into the final silicon.

The second is the more global perspective where managers think about portability between the verification activities, and the reuse of the tests across their teams and future projects. What is nice about the Breker approach is that we can satisfy both short-term requirements and longer-term perspective.

What is special about Breker that allows you to differentiate against big three competition?

Breker has been at this for 12 years. In this time, we have worked with many of the world’s leading semiconductor verification teams. These engineers have driven a whole solution approach, driving us to introduce practical features that save them time and energy.

For example, others will generate some high-level tests for Software Driven Verification. To mount these software tests on a processor requires extra work to make up for the lack of OS services, such as memory allocation and handling register access. We have automated this layer to eliminate this issue. The same is true of our UVM flow and post silicon. We also have advantages in the modeling area, use of the tools for debug, and coverage and profiling.

Has Accellera’s Portable Stimulus Standard helped move the chip design verification community closer to adopting Portable Stimulus tools?

Oh yes, clearly. For a number of years, we have been working with power users who were unconcerned with developing models using the Breker proprietary language based on C++. Indeed, our original language is more advanced than the standard. It has procedural as well as declarative constructs, and our power users are still actively employing it. However, to allow mainstream users to enjoy the benefits of these tools, they had to be assured that models they develop could be supported by multiple vendors, and this is where the standard has proven useful. We have seen a significant uptick in our business from the mainstream market as a result of its release last June. We fully expect it to overtake other verification languages over the next few years as it matures.

What tips can you give to entrepreneurs who are just starting out?

Start the journey if you have a good understanding of the end-user market and feel that you have something of value for them. In industries like ours where barriers of entry are high, innovative, compelling solutions are keys to success. A few other mantras we live by: take a user-centric approach to building solutions, treat your team like your family, and go out there and have fun. There will be many days where the end of the road is not visible. Be patient and believe in your journey. Eventually the world will converge.

What’s the status of Breker today, and what’s next for the company?

Breker is doing well. We witnessed dramatic growth in our business over the last two or three years, and hired the best and brightest as our team grows to meet this demand. Apart from all the general verification flows, we are seeing more specialized uses for the technology, an interesting development. For example, we are working on ISO 26262 automotive flows and find that requirements for this segment are easily specified to allow a full coverage test against them, a significant benefit. We offer TrekApps for ARMv8 integration testing, and now see interest in a similar platform for RISC-V with enhancements to allow for instruction set extensions. Security is another area where our tools can play an expanded role, providing powerful all-inclusive tests that attempt to find security holes. The list is endless and, right now, the verification world appears to be our oyster!

Editor’s Note:Breker will showcase the full complement of Trek5’s feature-rich set of expanded capabilities that go beyond Portable Stimulus test suite generation in Booth #701 during DVCon US next week (February 25-27, DoubleTree Hotel, San Jose, Calif). It will demonstrate practical applications of portable stimulus with examples of how PSS can be applied to accelerate UVM coding for complex blocks and SDV for large SoCs.

Applications for Breker’s Trek5 will be profiled throughout DVCon:

- Adnan Hamid, Breker’s chief executive officer, will be a panelist on “Verification and Compliance in the era of open ISA –– Is the Industry ready to Address the Coming Tsunami of Innovation?” The panel will be held Wednesday from 8:30 a.m. until 9:30 a.m.

- “Product Life Cycle of Interconnect Bus: A Portable Stimulus Methodology for Performance Modeling, Design Verification, and Post-Silicon Validation” will be presented by Gaurav Bhatnagar, staff engineer at Analog Devices. He will discuss a PSS methodology using Trek5 during the “Applications of the new Portable Stimulus Standard” session Wednesday from 10 a.m. until noon.

- Breker and Willamette HDL will offer a workshop titled, “Using Portable Stimulus to Verify an ARMv8 Sub-System Integration on an SoC,” Thursday from 1p.m. until 2:30 p.m. It will include an overview of the Accellera PSS language and a detailed plan for verifying an ARMv8 sub-system integration using Trek5.

Also Read:

CEO Interview: Cristian Amitroaie of AMIQ EDA