In this third article about China’s role in the global semiconductor industry I analyse the current state of affairs of the Chinese semiconductor industry in different segments. In the previous articles, I looked at the possible effects of a US-China decoupling in the semiconductor industry and the impact of the Big Fund and Chinese investments in semiconductor R&D. Both articles are available in Chinese as well: decoupling, Big Fund (文章翻译成中文: 脱钩, 大基金). In my next article that will be published soon, I will give an updated analysis of the impact of the US-China tech war on the semiconductor industry.

China aims to accelerate the development of the domestic semiconductor industry and reduce the reliance on imports of chips. But the semiconductor industry’s global value chain spans a wide variety of segments such as equipment, materials, software, design, manufacturing, assembly and testing.

One of the conclusions of my previous article was that Chinese (government) investments are often focused on increasing manufacturing capacity and acquiring existing technology instead of real new technology development. Besides having fabs to actually make chips, the tools and equipment needed for chip manufacturing and testing, the software needed to design chips, and the design capabilities themselves are all important in the semiconductor value chain.

In this article I look at the position of (mainland) China, the United States (US), and the rest of the world (ROW) in five different segments of the semiconductor value chain: equipment (EQP), Electronic Design Automation software & Intellectual Property core (EDA & IP), design/fabless & Integrated Device Manufacturer (DES & IDM), foundry (FOU), and Outsourced Semiconductor Assembly & Test (OSAT).

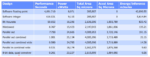

Table 1 shows the combined revenues of the major companies in these five segments for each of the three regions. I included the sales data of 136 companies: 27 equipment (6 from China, 13 from the rest of the world, and 8 from the United States), 9 EDA and IP (1 CN, 4 ROW, 4 US), 76 design and IDM (30 CN, 23 ROW, 23 US), 12 foundry (4 CN, 7 ROW, 1 US), and 12 OSAT (5 CN, 6 ROW, 1 US). Sales data is available from the annual report for listed companies, but unfortunately there are quite some relevant semiconductor companies that are not listed (e.g., Arm, GlobalFoundries, HiSilicon, Kioxia, Mentor Graphics, UNISOC). For 15 of those I based the sales data on publicly available information. For another 65 companies no sales information was available so they are not included in the analysis, which means the consolidated numbers in this article are a lower limit of the actual numbers. I would like to emphasise that the list of companies mentioned in this article is by no means exhaustive, but I believe it provides a representative overview of the global semiconductor value chain (with the materials segment excluded). As the objective of this article is to provide an overview of the Chinese semiconductor industry, I included more (and smaller) companies from China. For the rest of the world and the United States I included only the largest and most important companies. (i)

Table 1: Semiconductor sales by segment and region.

If we look at all sales data across five segments the whole semiconductor industry combined sales is US$ 571.8 billion. US headquartered companies account for 47%, companies from the rest of the world for 45%, and China based companies for 7%. For all three regions, design & IDM is the segment with highest sales. Globally, design & IDM accounts for 71% of all sales, followed by equipment (13%) and foundry (10%). OSAT (5%) and EDA and IP (2%) generate considerably less revenue.

China is relatively strong in OSAT, mainly because of JCET which accounts for 57% of China’s revenue in this segment. For EDA & IP and especially equipment, China is far behind the United States and rest of the world. The rest of the world region’s strongest segment is foundry, because of TSMC (78% of the region’s foundry revenue) and UMC (11%) from Taiwan. In addition, the rest of the world region is leading in OSAT, again because of Taiwanese companies such as ASE (73% of the region’s OSAT revenue) and PowerTech (12%). The US’ main strengths are in design & IDM and EDA & IP. Intel is the world’s largest semiconductor company based on revenue (US$ 72 billion) and Micron, Qualcomm and Broadcom all have more than US$ 20 billion sales. For EDA software all three global leaders are US headquartered: Synopsys, Cadence Design Systems, and Mentor Graphics (owned by German Siemens). Equipment is a narrow victory by the rest of the world region, led by Dutch ASML (#2 equipment company globally) and Japanese Tokyo Electron (#3), over the US, with Applied Materials (#1), Lam Research (#4), and KLA (#5).

Figure 1 also represents the sales data and includes all companies that account for at least 10% of sales of their segment in their own region.

Figure 1: Semiconductor sales by segment and region.

Further breaking down the revenues for rest of the world gives the following ranking (sales above US$ 10 billion):

- United States, US$ 270.9 billion

- Korea, US$ 80.9 billion

- Taiwan, US$ 75.9 billion

- Japan, US$ 50.0 billion

- China, US$ 41.3 billion

- The Netherlands, US$ 25.4 billion

Korea is home to two of the largest IDMs, Samsung (#2, US$ 56 billion sales) and SK Hynix (#3, US$ 23 billion). In addition to the foundry and OSAT companies mentioned above, Taiwan is also home to design companies such as MediaTek, Novatek and Realtek. Japan’s strength is in equipment with Tokyo Electron, Dainippon Screen and Advantest, and IDM with Kioxia, Sony Semiconductors Solutions, and Renesas, amongst others. China’s largest semiconductor companies are design companies Unis and HiSilicon, foundry SMIC and packaging and test provider JCET. More than half of the Netherlands’ semiconductor revenue is generated by lithography equipment supplier ASML but ASM International (equipment, US$ 1.4 billion), NXP (IDM, US$ 8.9 billion) and Nexperia (IDM, US$ 1.4 billion) also contribute generously.

In the remainder of this article I will look at the five segments separately, with special attention for the performance of Chinese companies compared to the global leaders.

Equipment

Many different types of tools and equipment are needed to make chips. Important steps in the IC manufacturing process include lithography, ion implantation, deposition (e.g., CVD, PVD), etching, cleaning, and testing. The major equipment suppliers are from the US, Japan and the Netherlands, but China is also trying to develop its domestic semiconductor equipment industry.

The lithography equipment segment is dominated by Dutch ASML with a market share of 85% and the only relevant competitors are Canon and Nikon from Japan. China’s sole lithography equipment maker is Shanghai Micro Electronics Equipment (SMEE) and its most advanced tool at present enables 90nm chip production. ASML sold their first lithography systems that could produce complex 90nm chips in 2004 already (16 years ago!).

For the deposition equipment segment there are more competitors. Some of the big players are active in PVD and CVD such as Applied Materials (US), Tokyo Electron (JP) and Lam Research (JP), but also smaller companies such as Aixtron (DE), ASM International (NL), Evatec (CH) and Ulvac (JP). NAURA, resulting from the 2017 merger between Sevenstar Electronics (established in 2001) and Beijing North Microelectronics (NMC, also 2001), is the largest semiconductor equipment company in China and active in this field.

Another more established Chinese equipment company is Advanced Micro-fabrication Equipment (AMEC). The Shanghai-based company that produces etch equipment and MOCVD tools was founded in 2004 and was in the first batch of companies to get listed on the new Shanghai Stock Exchange Science & Technology Innovation Board (or STAR Market) in 2019. Qualcomm participated in AMEC’s B round in 2007 and is still one of its shareholders. AMEC’s etch equipment is verified by TSMC for its 7nm process.

Other companies active in cleaning, packaging and testing equipment include Advantest (JP), ASM Pacific Technology (SG), Dainippon Screen (JP), and Teradyne (US). More Chinese semiconductor equipment companies worth mentioning are Hangzhou Changchuan Technology, Kingsemi, and PNC Process Systems but their revenues are well below US$ 150 million.

Table 2: Semiconductor equipment companies’ sales and R&D spending per region.

EDA & IP

Electronic Design Automation software and IP core is another area where China still lags far behind. The vast majority of the Chinese EDA market is taken by the three global leaders Synopsys, Cadence, and Mentor. There are some Chinese companies active in the EDA segment though, such as Cellix, Empyrean, ProPlus, Semitronix, and Xpeedic. Empyrean seems to lead the Chinese domestic field, but I could not find financial information for any of these companies. Cellix is reported to be preparing for a listing on the STAR market and ProPlus closed an investment round in April 2020 in which Intel reported it participated.

Table 3: EDA software & IP core companies’ sales and R&D spending per region.

An IP core is intellectual property of a licensing party that can be used as a building block for chip design. IC design companies use third party IP and their own IP to design their chips. The leading company in this field is UK-based but Japanese (Softbank) owned Arm Holdings. Basically, all smartphones and most IoT devices use Arm’s processor architecture. Softbank closed the Arm acquisition in September 2016, and just 1.5 years later, in April 2018, Arm China (also known as Arm mini China) was created. Arm China is 51% controlled by a consortium of Chinese investors and Arm owns 49%. Arm China sells and licenses Arm (UK) technology in China but has also gradually moved to developing its own (Chinese) IP. For example, Arm China has developed a design that allows Chinese-made chips to run a cryptographic algorithm built by China’s State Cryptography Administration.

Imagination Technologies is also UK-headquartered but was acquired by Cayman-based and Chinese funded private equity fund Canyon Bridge in November 2017. In April 2020 Imagination announced plans to appoint new board directors from China Reform Holdings, the major investor in Canyon Bridge. After the UK government expressed concerns this proposal was withdrawn. Imagination mainly develops IP for Graphic Processor Units (GPUs). Apple used to be Imagination’s biggest customer until 2016 and earlier this year they signed a new multi-year license agreement under which Apple will have access to a wider range of Imagination’s IP.

Previously mentioned Synopsys and Cadence are also active in the IP core licensing field, and so is US-based Rambus, mainly licensing memory technology. In China, VeriSilicon is the leading (but loss making) company in this field. Established in 2001, it’s investors include Intel, Samsung, Xiaomi, the Big Fund, and Walden International. VeriSilicon has announced the intention to list on Shanghai’s STAR market.

Besides the Arm architecture, there are only a few other processor architectures. Like Arm, MIPS and RISC-V are so called RISC (Reduced Instruction-Set Computer) architectures and x86 is a CISC (Complex Instruction-Set Computer) architecture. In general, CISC is more suitable for high performance processors (complexity and speed; e.g., servers) and RISC for power efficiency (e.g., smartphones).

MIPS Technologies developed the MIPS architecture in the 1980s and licensed it to chip designers. Imagination Technologies bought MIPS Technologies in 2013 and sold it to US based Wave Computing prior to the Canyon Bridge acquisition of Imagination in 2017. Wave Computing filed for bankruptcy in April 2020 but there are reports that MIPS will continue its business independently. MIPS is not nearly as successful as Arm but in China it is used by Loongson (formerly known as Godson and creator of China’s first domestic CPU) and Ingenic (designing CPUs and IoT and wearables chips).

RISC-V is an open source project that started at UC Berkeley in the US in 2010 and aims to provide royalty free instruction set architectures. RISC-V started in academia but in 2015 the RISC-V Foundation was established to create a community for standardisation and improvement through open collaboration. In March 2020 the RISC-V International Association (RVI) was incorporated in Switzerland after reflecting on the geo-political landscape and to calm “concerns of political disruption to the open collaboration model”. RVI mentions explicitly on its website that “there have not been any export restrictions on RISC-V in the US and we have complied with all US laws. The move does not circumvent any existing restrictions, but rather alleviates uncertainty going forward.” RVI has never received or pursued funding from any government and currently has more than 500 members, including Alibaba, Huawei, the Institute of Computing Technology of the Chinese Academy of Sciences, and VeriSilicon from China. US members include Western Digital, Nvidia, and Rambus. RISC-V is relatively new so no major competition for Arm yet, but the community is moving fast and in the current geopolitical climate open source, which is not export-controlled by definition, may be the way forward for Chinese chip design companies.

Design & IDM

For this article I combined the fabless design companies and Integrated Device Manufacturers in one segment as they all have the capabilities to design chips. The fabless design companies rely on foundries to manufacture the chips they designed, while IDMs make their chips in-house. Design & IDM is the largest segment of the semiconductor value chain across regions (72% of total semiconductor sales for China, 61% for rest of the world, and 81% for US); it also has the most companies included in this analysis for each region. The world’s biggest semiconductor companies are all active in this segment: IDMs Intel, Samsung, SK Hynix, and Micron, and fabless design companies Qualcomm and Broadcom. They all have more than US$ 20 billion sales; only foundry TSMC belongs to the same category with US$ 34.6 billion sales. Within the Design & IDM segment, the US is the clear leader with 54% of its sales, followed by the rest of the world with 39% and China’s 7%.

Table 4: IC design companies’ and IDMs’ sales and R&D spending per region.

The biggest Chinese chip design companies are Unis (also known as Unisplendour) an HiSilicon (fully owned by Huawei). HiSilicon develops SoCs (System on a Chip; multiple components such as CPU, GPU, and memory on one chip) based on Arm architecture. HiSilicon designs smartphone chips (Kirin), server chips (Kunpeng), and smartphone modems (Balong). The newest Kirin 810 outperformed competitor Qualcomm’s Snapdragon 855 SoC in the AI Benchmark test. Qualcomm is the global market leader in smartphone SoCs and has held the same position for the China market for a long time. Until Q1 2020 when HiSilicon led the China smartphone SoC shipments ranking for the first time. COVID-19 has a big impact though, as smartphone SoC shipments decreased more than 44% compared to Q1 2019.

Unis is part of the Tsinghua Unigroup ecosystem. Unigroup’s subsidiaries include fabless companies Pango Microsystems, Tongxin Microelectronics, Unic Memory, Unigroup Guoxin, UNISOC (formerly known as Spreadtrum), and Unis; foundries UniIC Semiconductors, XMC and YMTC; and OSAT company Unimos. Unis and Guoxin are listed companies. UNISOC primarily designs entry-level smartphone and feature phone chips, which are very popular in India and Africa.

Another Chinese State-Owned Enterprise (SOE) that is very active in the semiconductor industry is China Electronics Corporation (CEC). CEC’s companies include fabless Anlogic, CE Huada Tech, Huada Semiconductor, Microne, Phytium Technology, Shanghai Belling, Solantro (a Canadian company acquired in 2018 and now known as Huada Semiconductor North American R&D Centre), and Solomon Systech; foundry GTA Semiconductor; and OSAT company Chipadavanced. CE Huada Tech, Shanghai Belling, and Solomon Systech are listed companies.

Chinese consumer electronics company (and smartphone vendor) Xiaomi has been active in chip design with its subsidiary Pinecone established in 2014. Early 2017 Pinecone revealed the Surge S1 chipset, but Xiaomi’s 5C smartphone which used the S1 failed because of high power consumption and heat output. In April 2019 Xiaomi announced it would spin off and take a 25% stake in a new company Big Fish Semiconductors to focus on the development of AI and IoT chips. Pinecone (51% owned by Xiaomi and 49% by China’s Datang Telecom) will keep developing smartphone chips. Xiaomi also invested in IP provider VeriSilicon and is its second biggest shareholder behind the Big Fund.

The Chinese design companies mentioned above mainly use Arm architecture but some Chinese companies work with x86 architecture. Because x86 is a CISC architecture, it is the dominant architecture in the server market. Recently though, Arm and RISC-V based processors seem to get some more traction. Intel is market leader in the x86 processor market but AMD (also from the US) has been gaining market share over the last years thanks to its Ryzen chip architecture. Besides them, only VIA Technologies from Taiwan has a x86 CPU license but VIA has not been successful at making the products to get closer to Intel and AMD’s market share.

Interestingly though, on May 8 the first Chinese PCs with domestically developed x86 CPUs were released. They use the KX6000 processor series made by Zhaoxin, a joint venture between VIA Technologies and the Shanghai local government established in 2013. The performance of these KX6000 processors, which are based on architecture developed by VIA’s US subsidiary Centaur Technology, is still far behind Intel and AMD’s current offerings, but it’s definitely suitable for its intended government use. This is an important step in China’s plans to reduce dependence on foreign technology and Zhaoxin has ambitious plans to bridge the gap with Intel and AMD.

AMD also set up a joint venture in China, with partners including high performance computing maker Sugon and the Chinese Academy of Sciences. Tianjin Haiguang Advanced Technology Investment Co (THATIC or Higon), set up in 2016, actually comprises two JVs with AMD holding 51% shares of Chengdu Haiguang Microelectronics Technology (also known as HMC) and 30% of Chengdu Haiguang IC (also known as Hygon). AMD exported IP to subsidiary HMC and Hygon would customise the designs before they were sent to GlobalFoundries in the US for manufacturing. This allowed the Chinese side to call the processors ‘Chinese’ and AMD to comply with all relevant export control legislation. Until June 2019 that is, because then the US government added AMD’s JVs to the Entity List because Sugon had acknowledged military end uses and end users of its high-performance computers. The consequence is that US companies need to apply for a license before exporting products and technology to these entities and the US government follows a ‘presumption of denial’ policy.

Intel set up a collaboration with Tsinghua University and Montage Technology in 2016. Based on Intel’s x86 Xeon architecture and Tsinghua developed technology, Montage designed the Jintide CPU. Montage Technologies is listed on Shanghai’s STAR market since July 2019 and Intel owns 9% of its shares.

One Sino-American collaboration in the semiconductor industry that did not last long is the joint venture Qualcomm set up in 2016 with the Guizhou provincial government. The JV, Huaxintong Semiconductor Technologies (HXT), 55% owned by Guizhou province and 45% owned by Qualcomm, focused on designing server chips based on Arm architecture. In November 2018 HXT announced that the StarDragon 4800 had started mass production. This processor is similar to Qualcomm’s Centriq 2400 series with a modified crypto module to meet China’s commercial cryptographic algorithms standards. In April 2019 it was reported that the joint venture would shut down.

RISC-V architecture is another area where Chinese companies have become increasingly active. Alibaba Group acquired Hangzhou C-Sky Microsystems in 2018 and reorganised its chip R&D activities into Pingtouge Semiconductor (also known as T-Head). In July 2019 Pingtouge announced it developed a 16-core Xuan Tie 910 RISC-V CPU (XT910) and claimed it was the most powerful design based on RISC-V IP yet. Two months later Alibaba also announced the Hanguang 800 AI inference chip made with TSMC’s 12nm process. The Neural Processing Unit (NPU) is capable of handling complex tasks such as product search, image analysis, and personalised recommendations on Alibaba’s e-commerce platforms.

Foundry

The semiconductor pure play foundry segment is dominated by the rest of the world region, mainly because of Taiwan’s TSMC, the world leader in this field by far. The number two (UMC) and three (Vanguard) foundries from the rest of the world region are also based in Taiwan. The only US-based foundry is Abu-Dhabi owned GlobalFoundries and in China the largest foundries are SMIC and Huahong Grace. For some other Chinese foundries such as Huali (also from Huahong Group), YMTC and XMC (both part of Tsinghua Unigroup), and CXMT, I have not found financial data.

Table 5: Foundry sales and R&D spending per region.

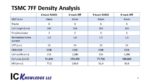

SMIC has made quite some progress over the years and is now capable of 14nm mass production, although the defect rates are still very high according to some sources. Industry leader TSMC and IDM Samsung are already mass producing 7nm (and TSMC starting 5nm), while GlobalFoundries announced it stopped 7nm development because of the high costs involved. On May 11 it was announced that SMIC had started mass production of Huawei/HiSilicon’s Kirin 710A on its FinFET 14nm process. Although these chips are not current state-of-the-art (Kirin 710 was launched in July 2018), this is a significant development for China’s semiconductor industry as it is the first time that Huawei uses a foundry other than TSMC to make its smartphone chips.

Other Chinese foundries, focused on developing memory chips, are YMTC and CXMT. The memory market is dominated by Samsung and SK Hynix from Korea and US-based Micron. On April 13, YMTC announced it has developed 128-layer 3D NAND flash memory chip X2-6070, based on its own Xtacking architecture. Whether X2-6070 will indeed be a success depends on multiple factors, including the timing of mass production (probably H1 2021) and yield (the proportion of chips on a wafer that work properly). So after designing the memory chip, getting the production process right will be the next big challenge for YMTC.

CXMT, China’s new DRAM memory maker (established in 2016, then known as Innotron), announced at the end of April that they signed a long-term patent license agreement with US-based Rambus to get access to a wide variety of DRAM patents. This deal will strengthen and diversify CXMT’s IP portfolio. Through previously signed licensing agreements, CXMT already has access to Qimonda’s IP (Qimonda spun off from Infineon in 2006 and was the world’s second largest DRAM company at the time but ceased operations in 2011).

OSAT

Half of the top 10 global Outsourced Semiconductor Assembly and Test (OSAT) companies are from Taiwan. Market leader ASE Group’s market share is 47%, followed by Amkor from the US and JCET from China. With the other 4 Taiwanese companies, two Chinese companies (TFME and Tianshui Huatian) and one Singaporean company complete the top 10.

Table 6: OSAT companies’ sales and R&D spending per region.

This analysis shows that China is still a relatively small player in the global semiconductor value chain, except for the OSAT segment where China holds more than 20% of the global market. There are 3 Chinese companies in the global top 6 OSAT companies, while 6 years ago only JCET made the top 10. This also shows that the developments in the Chinese semiconductor industry can go fast.

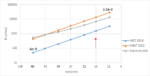

However, in other segments, particularly semiconductor equipment and EDA & IP, China is still far behind. Although AMEC has developed tools which are used in many foundries, AMEC is still a small player (around #20) among all the semiconductor equipment makers ranked by revenue. And size matters. To stay competitive in the semiconductor industry, companies need to invest in R&D and with higher sales companies can invest more in new technological developments and innovation.

Table 7: Average R&D investment as percentage of sales across segments and regions.

There are no huge differences between the three regions when it comes to companies’ average R&D spending as percentage of sales. American design & IDM companies spend more on R&D than their competitors from China and the rest of the world, and Chinese foundry and OSAT companies on average spend a larger part of their revenue on R&D than others. For the foundry segment, this is mostly attributable to SMIC’s R&D spending (22.1%) which is much higher than any other foundry in the world (Chinese Silan ranks second with 10.7% and TSMC is third with 8.5%). Looking at the actual R&D expenditures (in dollars), China’s share of global R&D expenditures is indeed higher than its share of global sales for the foundry (18% vs 8%) and OSAT (23% vs 21%) segments. However, for both these segments the rest of the world’s R&D expenditures are much higher than those of China; for foundry the rest of the world region spends 4.6 times as much on R&D as China, and for OSAT they spend 2.9 times as much.

For the equipment and EDA & IP segments there are no apparent differences between regions (and like for foundry and OSAT, the sample sizes on which these averages are based are small) but for design & IDM, US companies on average spend a higher percentage of their revenue on R&D than others. Because these are also the biggest companies in the whole industry, measured by sales, this is a major competitive advantage of the American semiconductor industry. Although US design & IDM companies account for 54% of global design & IDM sales, they are responsible for 72% (or a combined US$ 38.9 billion for the 22 companies included in this analysis) of global R&D expenditures in this segment. The amount of money Intel spends on R&D, US$ 13.4 billion, is higher than the annual revenue of all semiconductor companies in the world except 8 (Samsung, TSMC, Qualcomm, Micron, SK Hynix, Broadcom, Applied Materials, and Texas Instruments).

The absence of major differences in R&D spending as percentage of sales between regions for the equipment and EDA & IP segments does not mean that it will be easier for China to catch up in these areas. For example, ASML spends around US$ 2.2 billion on R&D, which is twice the annual revenue of all six Chinese semiconductor equipment companies included in this analysis combined. For EDA the whole industry basically depends on the three major vendors Synopsys, Cadence, and Mentor. Although quite a few Chinese companies are developing EDA tools, none of them are competitive as they are not comprehensive enough (no complete design flow) and because the most advanced fabs and foundries will not use them, it is extremely difficult for them to get a better understanding of the processes and improve their software.

Fortunately for China, some developments provide a more positive outlook for growing the domestic semiconductor industry. The establishment of Arm China, the acquisition of Imagination Technologies, Intel investing in Montage Technology and ProPlus, the IP licensing deal between Rambus and CXMT, and the whole development of the RISC-V movement, could bring opportunities to strengthen China’s semiconductor industry. In the chip design field, HiSilicon is already world class and entered the top 10 of semiconductor sales leaders for the first time in Q1 2020 according to IC Insights. Recent achievements including Zhaoxin’s first domestically developed x86 CPU, Pingtouge’s RISC-V based CPU and AI inference chip, and YMTC’s 3D NAND flash memory chip, indicate progress is certainly being made in Chinese chip design. The recent announcement that SMIC is mass producing HiSilicon’s Kirin 710A on 14nm FinFET is a significant development for China’s chip manufacturing.

But… the challenges for particularly the equipment and EDA segments remain, and it is extremely difficult to catch up with industry leaders (also in design and manufacturing) when they spend much more on R&D and thus maintain their technology leadership. The establishment of the Big Fund is one (small) step to help Chinese semiconductor companies to overcome this gap, and recently there seems to be a trend for more Chinese semiconductor companies to go public, for example on Shanghai’s STAR market. AMEC and Montage Technology are already listed there, SMIC, VeriSilicon and Cellix announced plans to do so, and Imagination Technologies, UNISOC, and Horizon Robotics are also rumoured to file for an IPO. Although companies understandably look for more funding and resources, they should also keep in mind that the interests of investors (quick returns) do not always align with those of the companies themselves (long term commitment to R&D). There are no quick wins for companies that still need to establish their position in the global semiconductor value chain.

And then of course the biggest stumbling block for the development of China’s domestic semiconductor industry is the current geopolitical climate and recent actions taken by the US government that restrict American, and since May 15, 2020 also non-American, companies from doing business with some Chinese semiconductor companies. I will write more about the impact of the US-China tech war on the semiconductor industry in my next article. So stay tuned!

I would like to end this article with a suggestion for further reading that really gave me a better understanding of the history and development of the Chinese semiconductor industry. It is very informative and I really enjoyed reading the article originally written by Boss Dai (戴老板), published on his WeChat account on May 15, 2018: 中国芯酸往事. The article is translated into English by Jeffrey Ding and Lorand Laskai and published in the July 8, 2019 ChinaAI newsletter: The Sour Past of “China Chips”.

Bart van Hezewijk

Officer for Innovation, Technology & Science

Netherlands Innovation Network

Consulate-General of the Kingdom of the Netherlands in Shanghai

@bartvanhezewijk

(i) Note on data collection

For this analysis of the global semiconductor value chain I identified 201 companies: 100 from China, 59 from rest of the world, and 42 from the US. 121 of these companies are listed so I could get their sales and R&D spending data from their annual reports. The annual report used is the report for the fiscal year ending 31 December 2019 or earlier that year, except for Aixtron, Goodix, JCET, PowerChip, Tower Semiconductor (31 Dec ‘18), Ambarella (31 Jan ‘20), and Marvell (1 Feb ‘20).

For another 15 companies I used other publicly available data:

- Arm (Softbank Group Annual Report 2019), Cambricon, GlobalFoundries, Imagination Technologies, Kioxia, Nexperia, Vanguard International Semiconductor (VIS Consolidated Financial Statements), and VeriSilicon.

- For GalaxyCore, HiSilicon, Huada Semiconductor, Integrated Silicon Solutions Inc, Sanechips Technology, and UNISOC: Trendforce (2018 revenue).

- For Mentor Graphics I calculated the 2019 revenue relative to Synopsys’ and Cadence’ 2019 revenue, based on their share of their combined revenues (Synopsys 46%, Cadence 33% and Mentor 21%) in 2016 and 2017 (latest available annual reports of Mentor).

For some companies their semiconductor business is a part of their total business. For these companies I only included the semiconductor revenue:

- Fujitsu Semiconductor: LSI Devices within Device Solutions, 5.3% of Fujitsu Group total revenue.

- Hitachi Hitech: Electronic Device Systems, 20.1% of total revenue.

- IBM: Systems (includes Servers & Storage Systems), 9.9% of total revenue.

- Jusun Engineering: Semiconductor (Display and Solar Cell not included), 52% of total revenue.

- Mitsubishi Electric: Electronic Devices, 4.4% of total revenue.

- Samsung: Semiconductor within Device Solutions (inter-company revenue not included), 28% of Samsung Electronics total revenue.

- Tianjin Zhonguan: Semiconductor Device (Semiconductor Materials and New Energy not included), 0.83% of total revenue.

- Wonik IPS: Semiconductor (Display and Solar not included), 55% of total revenue.

Some large companies that are active in the global semiconductor value chain are left out from the data analysis because they do not report financial data for their semiconductor related business or their data was not specific enough to be included in this analysis, e.g., Apple (US, DES), Baidu (CN, DES), Bosch (DE, DES), Canon (JP, EQP), and Nikon (JP, EQP).