Does this justify the widespread Intel bashing?

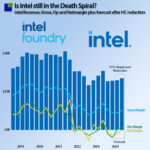

The latest Intel earnings release was another sharp and deeper turn into the company’s death spiral. On the surface, it is just a whole load of bad news, and the web has been vibrating with Intel bashing since the release.

So what are the facts?

From a revenue perspective, Intel was inside the guidance, but the $12.8B was less than the midpoint guidance of $13B.

The Gross Margin was a miss. Intel delivered 35.4% versus the guidance of 40.2%, resulting in a Gross Profit of $4.5B versus guidance of $5.2B midpoint guidance. While 700M$ less gross profit is significant, the context is that Intel is in a pickle; Intel has clearly stated that 2024 is not the recovery year.

An internal move of product between factories impacted the result negatively but will bring long term benefits – a sign Intel is now ready to make tough decisions.

David Zinsner, Intel’s CFO, commented on the miss:

“Second-quarter results were impacted by gross margin headwinds from the accelerated ramp of our AI PC product, higher than typical charges related to non-core businesses and the impact from unused capacity,” said

The next two quarters will show minimal revenue growth and further profitability challenges.

I will let people respond the way they want, but from my perspective, this miss does not change anything about Intel’s current situation. The company was in a death spiral before and is still in a death spiral.

Intels Death Spiral

Intel’s current situation is not rooted in the company’s near-term strategy but rather due to historic decisions coming home to roost.

In late 2019, the long-term revenue growth stopped, while Intel continued to deliver rich results that kept everybody satisfied while milking the cow. In 2022, the cow got sick and was struggling to provide the necessary nutrition to Intel.

Intel is a manufacturing company that needs significant profits to fund the Capital Investments required to maintain and expand its manufacturing assets.

Q3 and Q4-24 Forecast

From a manufacturing technology perspective, Intel chose the wrong path, believing it could maintain its technology leadership without using the Deep UV tools that other companies, most notably TSMC, had decided to use.

Even though the IFS revenue increased, the external IFS revenue is still embryonic. Intel disclosed that the external deal funnel is meaningful at $15B, although this is hard to resolve regarding revenue.

Combining the Internal and External IFS revenue still leaves a distance to the 500-pound gorilla in the Foundry.

The Intel IFS challenge is still massive

From a product perspective, Intel has been blessed by owning the largest cow in the industry. The client business supports CPUs for the important PC segment. The drawback is that the client division has been far too powerful and dominating the other divisions.

This is a classical corporate problem: corporations are locked into a single category despite having the resources to divest into other market areas.

Intel has often tried to divest into other areas but has failed. The company completely missed or failed to address the transformation of the Data Center market from CPUs to GPUs.

The Client Computing Group’s share of business has been reasonably stable over time, which also means that the Intel boat rises and falls with the PC market plus the CPU share of the data centre market.

The situation is bad but, in reality, unchanged from last quarter (within a few hundred M$). So, is the market’s response out of touch with reality?

Intel is taking action

Pat Gelsinger, in an internal memo, noted that headcount and results had drifted away from each other and it was necessary to take action.

“Our costs are too high, our margins are too low,” and explained why the workforce reduction is necessary. He noted that Intel’s annual revenue in 2020 was about $24 billion higher than the previous year, yet the workforce has grown by 10%.

The missed result and a visit from the head cutting experts McKinsey and friends have likely accelerated what was already brewing in the corner offices. It is time for difficult decisions:

Intel will reduce headcount by 15% during the next 6 quarters, which will significantly reduce Operational Costs. Capital Expenditures will also be reduced, which likely means delays to some of the investment activities. Fixed sales costs will be reduced by 1B$, and dividends will be suspended for now.

The Chart below shows our analysis of the Revenue and Operating Profits per employee with the projected effect of the headcount reduction program. We assume revenue growth is in line with the market, which certainly can be challenged both upwards and downwards.

The headcount cut is expected to bring Intel to a $20B$ capex in 2024, which suggests a 32% decrease from Q4-23 to Q4-24, as seen below.

This is significantly steeper than the 15% headcount cut suggested, which does not indicate it is the average wage employee who is getting fired.

There are other elements to OpEx besides pay, but it is safe to assume that pay is the major element. Not all pay is included in OpEx. The pay associated with the manufacturing of the products is included in the Cost of Goods Sold.

This discrepancy suggests that there is something else at play. It could be that the firing is higher in the ranks or people with longer tenure as both groups have higher than average pay. It could also be that Intel expects more people to leave than those fired. This could be done through a voluntary program that runs parallel with the firing process. Lastly, there could be serious pay cuts happening. When you are in a firing season, you could be very motivated to accept a pay cut.

Also, the decline in OpEx is happening a lot faster than generally during headcount reduction. It takes time for people to leave the payroll. Again,like some deal-m here, it seems aking is going on to get people off the payroll faster, potentially in the form of stock-related severance packages.

If Intel can pull it off without too much impact on revenue, the company will be back in the black and able to contribute to the long-term capital expenses that Intel is committed to.

The reduction in Capital Expenses

In the conference call, Intel revealed that the CapEx budget would be cut by 20% in 2024 to $26B in 2024 and $21.5B in 2025. The new budget was presented interestingly as a Gross and Net CapEx budget.

As Intel’s profitability started the dance around the zero line beginning in 2022, the company was unable to finance the CapEx budget of the IDM 2.0 strategy through retained earnings and had to find alternate ways of funding the plan.

Banks would want a premium interest rate because of Intel’s risky situation, and diluting the stock while make the come deflated would back much more difficult. It was time to get creative.

Intels Masterstroke

The first part of Intel’s plan was likely political. It would be surprising if Intel were not the cornerstone of the 2022 Chips Act of the Biden Administration. The relationship between Intel and the administration was very visible, and Intel probably had an excellent idea of what they would get out of the Chips Act early.

A prerequisite for getting funding for a project was that it was new and on US soil, but the political relationship was important. Recently, AMAT has been denied funding, which could be for several reasons but coinciding with an investigation of back-door sales of Semiconductor tools to China without export licenses.

In short, Intel’s IDM 2.0 plan was perfectly aligned with the US administrations and like-minded governments in Europe.

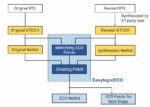

The second part of Intel’s plan was to attract equity investors without diluting the company’s value. Enter the SCIP: Semiconductor Co-Investment Program.

The SCIP program provides financial flexibility and strategic funding to support Intel’s manufacturing and expansion plans. It involves strategic partnerships with financial firms to co-invest in Intel’s semiconductor manufacturing facilities. This helps Intel manage its capital expenditures and maintain a strong balance sheet while expanding its production capabilities.

Intel has made two SCIP deals:

Fab 34 in Leixlip, Ireland, with Apollo, and the expansion of the Ocotillo Campus in Arizona with Brookfield. Both deals involve a 51/49% ownership structure in Intels favour.

These deals, combined with the Chips Act funding and other subsidies, are a complete master stroke for which Intel and Pat Gelsinger have not received sufficient credit. In a situation where Intel lacked funding, and it would be expensive to borrow, the SCIP rabbit was pulled out of the hat:

The illustration above illustrates the outcome of the $53B$ investment in the two fabs. For an investment of approximately 1/3rd of the total needed for the two fabs, Intel managed to get 51% ownership and 100% control. That can only be seen as a very impressive way of getting out of the corner Intel was in.

The bill for these deals will be the sharing of the manufacturing margin with the two financial partners – this is a small price compared to failing the manufacturing strategy.

Intel is still in a Death Spiral, but management has shown the ability to make tough decisions and has found creative ways to finance the incredibly expensive fabs. This is very important as there will be more difficult decisions ahead.

A key element will be Intels ability to execute the company’s product strategy in the AI PC market and in both the CPU and GPU parts of the Datacenter market. Next weeks post will be a business overview of the Datacenter market.

Also Read:

TSMC’s Business Update and Launch of a New Strategy

Has ASML Reached the Great Wall of China

Will Semiconductor earnings live up to the Investor hype?