Keynote #2 at SNUG 2012 was John Cornish, VP Marketing at ARM. Why they sent a marketing person to speak in front of 2,000+ engineers I do not know. To top that, next time they should send a sales person and do a real dog and pony show. To find out more about John I checked his LinkedIn profile which was bare. So enough about John, lets hit on the key points of his presentation:

[LIST=1]

Besides pointing out the obvious, John did share some interesting data about Angry Birds and CPU usage. Apparently starting up the game is the big CPU draw but actually playing it, not so much CPU is required. That chart probably tracks with the human brain and how much intelligence is consumed during the same process.

ARM is pushing the big.LITTLEpower management strategy where you have a little core managing resources while the big cores are only used when required. For example, the NVIDIA Tegra 3 has four big cores and one little core. The ARM Mali GPU is also big.LITTLE. Mike Demler did a nice write up of Mali HERE.

big.LITTLE processing has been designed to deliver the vision of the right processor for the right job. TheCortex-A15 processoris the highest performing, low-power ARM processor ever developed, while theCortex-A7 processor is the most energy efficient ARM application processor ever designed…

As an undergrad computer science guy this was known to me as master/slave or asymmetric processing versus a more intelligent symmetric approach where the CPUs were granted equal status.

There was a lot more to John’s presentation but he lost me to a game of Words with Friends with my wife. I was on a 5 game winning streak so it was a hot and heavy competition, which I lost. My wife and I place some serious bets on these games so it required both my Big and Little processing units.

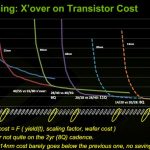

With the challenges of scaling 20nm and the coming mobile processor attack by Intel Atom using 22nm FinFet technology, I was hoping ARM would at least mention it. Dr. Greg Yeric, ARM Consultant Design Engineer did a talk on “IP Design and the FinFET Transition”, mentioned in my blog 3D Transistor for the Common Man!, which covered foundry access to finFETs so I know ARM is working on it. It would have been interesting to hear what the ARM SoC FinFet marketing strategy is, especially since the next SNUG keynote is Dr Chenming Hu, the father of the FinFet.

Here are two other FinFet blogs:

It will be interesting to see what happens at the TSMC 2012 Technical Symposium next month. My prediction is that we will see FinFets at 20nm as a mid-life kicker. IBM presented two FinFet papers at ISSCC this year so the Fab Club (IBM, Samsung, GLOBALFoundries) will not be far behind.

As far as trending search terms on SemiWiki: FinFets and 3D Transistors will continue to dominate this year, my opinion, so you will see more blogs on the subject, absolutely.