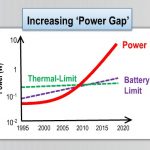

Power analysis and reduction for SoC designs is a popular topic because of our consumer electronics dominated economy, and the need to operate devices on a battery source for the maximum time before a recharge. Just from my desk I can see multiple battery-powered devices: Laptop, tablet, smart phone, e-book reader, bluetooth … Read More

Tag: webinar

Migrating to Andes from 8051

The 8051 microcontroller has been around for years…decades in fact. It was originally developed in 1980 by Intel. Back then it required 12 clock cycles per instruction but modern cores use just one. While it is still widely used, mostly as an IP core for SoCs, it is running out of steam despite running over 50 times faster than… Read More

Known Unknowns and Unknown Unknowns

Donald Rumsfeld categorized what we knew into known unknowns and unknown unknowns. In a chip design, those unknown unknowns can bite you and leave you with a non-functional design, perhaps even intermittent failures which can be among the hardest problems to debug.

Chips are too big to do any sort of full gate-level simulation,… Read More

Low-Power Design Webinar – What I Learned

You can only design and optimize for low-power SoC designs if you can actually simulate the entire Chip, Package and System together. The engineers at ANSYS-Apachehave figured out how to do that and talked about their design for power methodology in a webinar today. I listened to Arvind Shanmugavel present a few dozen slides and… Read More

Analog ECOs and Design Reviews: How to Do Them Better

One of the challenges in doing a complex analog or mixed signal design is that things get out of step. One designer is tweaking the schematic and re-simulating, another is tweaking the layout of transistors, another is changing the routing. This is not because the design flow is messed up, but rather it reflects reality. If you wait… Read More

Low-Power Design Analysis and Optimization for Mobile and High-Performance Computing Applications

For several decades now consumers like me have enjoyed using mobile devices including:

- Transistor radios, my first one had just 6 discreet transistors in the 1960’s

- HP 21 Calculator, used in college with Reverse Polish Notation, circa 1976

- Zenith Data Systems laptop, with two floppy drives, 1980’s

- Palm Pilot V,

Why Adopt Hierarchical Test for SoC Designs

IC designers have been creating with hierarchy for years to better manage large design sizes, however for the test world the concept of hierarchy and emerging standards is a bit newer. TSMC and Synopsys jointly created a webinarthat addresses hierarchical test, so I’ve attended it this week and summarized my findings here.… Read More

Today’s Program is Brought To You by the Letter A

What do nVidia, Freescale and GlobalFoundries have in common? They are semiconductor companies? They are ARM licensees? They are doing 28nm chips? They all have the letter ‘a’ in their names?

All true, but that’s not what I was thinking of. But the letter ‘a’ is a clue since Apache (and Ansys) begin with ‘a’. All three companies have… Read More

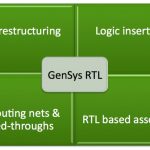

Derivative Designs Need Tools Too

Increasingly, SoC designs consist of assembling blocks of pre-designed IP. One special case is the derivative design where not just the IP blocks get re-used but a lot of the assembly itself. For example, in the design below some blocks are added, some blocks are updated, some hierarchy is changed. But the bulk of the design remains… Read More

Enabling 14nm FinFET Design

There’s never a dull moment in the foundry race to offer FinFET processes that enable leading-edge SoC design. Today I attended a webinar hosted by Samsung and Synopsys on how to enable 14nm FinFET design. The two speakers were Dr. Kuang-Kuo Lin from Samsung and Dr. Henry Sheng from Synopsys.

Dr. Kuang-Kuo Lin, Samsung

Dr.… Read More