While pushing Moore’s Law’s boundaries in the world of 2D packaging, companies are starting to explore nontraditional approaches towards designing integrated circuit chips. 2D packaging is currently the most used method in designing chips in the industry, and while it leads in efficiency of power and performance, it lacks … Read More

Tag: tsv

2.5D supply chain takes HBM over the wall

SoC designers have hit the memory wall head on. Although most SoCs address a relatively small memory capacity compared with PC and server chips, memory power consumption and bandwidth are struggling to keep up with processing and content expectations. A recent webinar looks at HBM as a possible solution.… Read More

Fabless vs IDM for Data Centers: Silicon Photonics as a Disruptive Force?

I recently received a copy of a book entitled Silicon Photonics III (Amazon) and while perusing the book I was captured by the first chapter entitled ‘Silicon Optical Interposers for High-Density Optical Interconnects’. The chapter covered the work of a team in Japan on an idea they termed “on-chip servers” and “on-board data … Read More

How HBM Will Change SOC Design

High Bandwidth Memory (HBM) promises to do for electronic product design what high-rise buildings did for cities. Up until now, electronic circuits have suffered from the equivalent of suburban sprawl. HBM is a radical transformation of memory architecture that will have huge ripple effects on how SOC based electronics are … Read More

2015 3D ASIP conference: Thar’s Gold in Them Thar Hills!

Last week I presented at the 3D ASIP EDA Tutorial and attended the Conference. In previous years, leading edge papers were presented from large companies pushing a solution to meet their needs. These companies had the resources and clout to achieve some astounding successes, but the lingering question was: “what other product… Read More

ASMC 2015 Preview

From May 3[SUP]rd[/SUP] to May 6[SUP]th[/SUP] the 26[SUP]th[/SUP] annual Advanced Semiconductor Manufacturing Conference (ASMC) will be held in Saratoga Springs, New York.

The ASMC offers a unique view of challenges to the semiconductor industry focusing on things like defect reduction, metrology and fab operations. In… Read More

TSV Modeling Key for Next Generation SOC Module Performance

The use of silicon interposers is growing. Several years ago Xilinx broke new ground by employing interposers in their Virtex®-7 H580T FPGA. Last August Samsung announced what they say is the first DDR4 module to use 3D TSV’s for enterprise servers. Their 64GB double data rate-4 modules will be used for high end computing where … Read More

Will 3DIC Ever Be Cheap Enough for High Volume Products?

More news from the 3DASIP conference. Chet Palesko of SavanSys Solution had an interesting presentation with the same title as this blog (although this blog draws from several other presentations too). Chet took a look at what aspects of 3D are likely to get cheaper going forward. He took as a starting point that stuff that is not … Read More

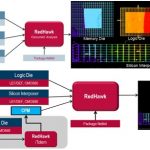

Solution for PI, TI & SI Issues in 3D-ICs

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

Noise & Reliability of FinFET Designs – Success Stories!

I think by now there has been good level of discussion on FinFET technology at sub-20 nm process nodes and this is an answer to ultra dense, high performance, low power, and billion+ gate SoC designs within the same area. However, it comes with some of the key challenges with respect to power, noise and reliability of the design. A FinFET… Read More