The founder of Mirabilis Design, Mr. Shankar has over two decades of experience in management and marketing of system level design tools. Prior to establishing Mirabilis Design, he held the reins as Vice President, Business Development at MemCall, a fabless semiconductor company and SpinCircuit, a joint venture of industry… Read More

Tag: systemc

ESL Expertise when You Need It. Spinning Up Faster

System-level expertise, once the domain a few architecture specialists, is now shouldering its way everywhere into chip design and verification. In virtual modeling together with OS and application software certainly. That now couples into mixed-level system-verification, using different levels of abstraction for different… Read More

Does IDE Stand for Integrated Design Environment?

As regular readers may know, every few months I check in with Cristian Amitroaie, CEO of AMIQ EDA, to see what’s new with the company and their products. In our posts so far this year we’ve focused on verification, and now I’m wondering how an integrated development environment (IDE) provides benefits to designers. They work on huge… Read More

SystemC Methodology for Virtual Prototype at DVCon USA

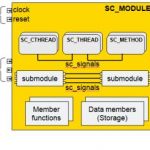

DVCon was the first EDA conference in our industry impacted by the pandemic and travel restrictions in March of this year, and the organizers did a superb job of adjusting the schedule. I was able to review a DVCon tutorial called “Defining a SystemC Methodology for your Company“, given by Swaminathan Ramachandran… Read More

DVCon Is a Must Attend Event for Design and Verification Engineers

Learning is a never-ending process for design and verification engineers, so outside of reading SemiWiki you likely want to attend at least a few events per year to keep updated, learn something new, attend a workshop, or even present something that has made your IC project work much better than before. Sure, DAC is always a great… Read More

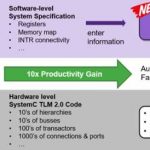

Update on SystemC for High-Level Synthesis

The scope of current system designs continues to present challenges to verification and implementation engineering teams. The algorithmic complexity of image/voice processing applications needs a high-level language description for efficient representation. The development and testing of embedded firmware routines… Read More

MENTOR at DVCON 2019

The semiconductor conference season has started out strong and the premier verification gathering is coming up at the end of this month. SemiWiki bloggers, myself included, will be at the conference covering verification so you don’t have to. Verification is consuming more and more of the design cycle so I expect this event to … Read More

Virtual Prototyping With Connection to Assembly

Virtual prototyping has become popular both as a way to accelerate software development and to establish a contract between system/software development teams and hardware development and verification. System companies with their tight vertical integration lean naturally to executable contracts to streamline communication… Read More

Mentor gets Busy at DVCon

You’d expect Mentor to be covering a lot of bases at DVCon and you wouldn’t be wrong. They’re hosting tutorials, a lunch, papers, posters, there’s a panel and of course they’ll be on the exhibit floor. I’ll start with an important tutorial that you really should attend, Monday morning, on creating Portable Stimulus Models… Read More

Getting out of DIY Mode for Virtual Prototypes

Virtual prototyping has, inexplicably, been largely a DIY thing so far. Tools and models have come from different sources with different approaches, and it has been up to the software development team to do the integration step and cobble together a toolchain and methodology that fits with their development effort.

That integration… Read More