Although semiconductor community has ushered into the era of SoCs, the verification of SoCs is still broken. There is no single methodology or engine to verify a complete SoC; this results in duplication of efforts and resources for test creation and verification at multiple stages in the SoC development, albeit with different… Read More

Tag: systemc

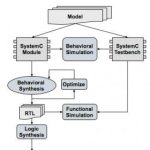

SystemC and Adam’s Law

At DVCon I sat in on a series of talks on using higher-level abstraction for design, then met Adam Sherer to get his perspective on progress in bringing SystemC to the masses (Adam runs simulation-based verification products at Cadence and organized the earlier session). I have to admit I have been a SystemC skeptic (pace Gary Smith)… Read More

Leveraging HLS/HLV Flow for ASIC Design Productivity

Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More

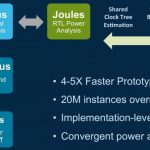

A New Unified Power Solution at All Levels

When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

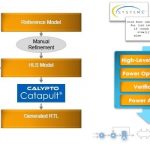

Choosing C++ or SystemC for High Level Synthesis

Most engineers learn by doing, and so at DAC in June an EDA vendor with High Level Synthesis (HLS) tools held a language tutorial on choosing C++ or SystemC for design and verification projects. The EDA company is Calypto, and Stuart Clubb put together the tutorial on using synthesizable C++ or SystemC. The design and verification… Read More

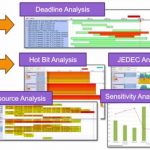

DDR stands for Don’t Do (Just) RTL

In optimizing SoC design for performance, there is so much focus on how fast a CPU core is, or a GPU core, or peripherals, or even the efficiency of the chip-level interconnect. Most designers also understand selecting high performance memory at a cost sweet spot, and optimizing physical layout to clock it as fast as possible within… Read More

Successful Venture of an Indian Global VIP Company

It’s rare that we find a truly Indian-based company operating globally in the semiconductor space. Although the ‘gold rush’ towards IP development in the last decade initiated many IP start-ups in India, today we rarely find Indian IP company names which are shining in the global arena. The story of services companies is different,… Read More

SystemC Co-Simulation of NoCs and IP Blocks

Verification in general suffers from a couple of fundamental problems. Availability of models and performance of different levels of representation.

The first problem, availability of models, is that you would like to start verification as soon as possible but all the representations are not ready early enough. Obviously … Read More

Ensuring Safety Distinctive Design & Verification

In today’s world where every device functions intelligently, it automatically becomes active on any kind of stimulus. The problem with such intelligence is that it can function unfavorably on any kind of bad stimulus. As the devices are complex enough in the form of SoCs (which at advanced process nodes are more susceptible to … Read More

HLS – Major Improvement through Generations

I am a believer of continuous improvement in anything we do; it’s pleasant to see rapid innovation in technology these days, especially in semiconductor space – technology, design, tools, methodologies… Imagine a 100K gates up to 1M gates design running at a few hundred MHz frequency and at technology node in the range of .18 to … Read More