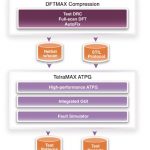

On my first job out of college as an IC design engineer I was surprised to discover that a major cost of chips was in the amount of time spent on the tester before being shipped. That is still true today, so how would you keep your tester time down, test coverage high and with a minimum number of pins when using multiple processors on a single… Read More

Tag: synopsys

Workload-tuned cores seeing greater interest

Is it possible to design a processor with very high performance and low power consumption? To answer that, embedded illuminati are now focusing on designs tuned to specific workloads – creating a tailored processor that does a few things very efficiently, with nothing extra.… Read More

Aart: Technomic Push-Pull

Aart de Geus gave one of the visionary look to the next 50 years of EDA as a warmup to Stephen Wu’s keynote. EDA is enabling the greatest push-pull ever, part of an exponential change on a scale never before seen.

Technologies seem to go through a 50 year technical push phase (driven by improving the technology) followed by a 50… Read More

Fujitsu, Mediatek, Richtek and Synopsys om Custom IC Design

Synopsys has been acquiring EDA and IP companies at a fast clip over the past few years and it’s often made me wonder how they are going to craft a coherent tool flow for custom IC design. At DACthis year I learned that for schematic capture the winning tool is Custom Designer SE– a relatively new tool, while the IC layout… Read More

Can we really find a way to speed-up Processor & DSP core designs?

Once upon a time, ASIC designers involved in Processor design, like I was, for the first time in 1987 for Thomson CSF and again in 1994 for Texas Instruments, at that time supporting height (8) ASIC designed by another French company, the Advanced Computer Research Institute (ACRI), had to re-invent the wheel almost every day. When… Read More

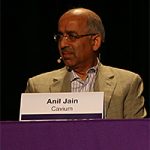

Deploying 14nm FinFETs in your Next Mobile SoC

At DAC in Austin a design company, foundry and EDA vendor teamed up to present their experiences with 14nm FinFETs during a breakfast on Tuesday.

Panelists included:

- Ed Sperling, Semi Mfg and Design

- Anil Jain, Cavium

- Subramani Kengeri, GLOBALFOUNDRIES

- Kelvin Low, GLOBALFOUNDRIES

- Raymond Leung, Synopsys

- Bari Biswas, Synopsys

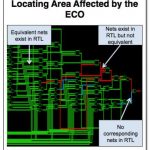

Formality Ultra, Streamline Your ECOs

One of the most challenging stages in an SoC design is achieving timing closure. Actually design closure is perhaps a better term since everything needs to come together such as clock tree, power nets, power budget and so on. Changes made to the design are known as ECOs (which stands for engineering change orders, a term that comes… Read More

AMS IC Simulation Update from Synopsys at DAC

Last year at DAC we didn’t really know the circuit simulation roadmap for Synopsys because of all the EDA company acquisitions, however this year it’s clear to me that:

- HSPICE continues on, although it’s a lower performance circuit simulator than FineSim

- FineSim from Magma is well-loved, and faster than HSPICE

First FinFETs Manufactured at #50DAC!

This was my 30[SUP]th[/SUP] DAC and the second most memorable. The most memorable was my second DAC (1985) in Las Vegas with my new bride. We had a romantic evening ending with ice cream sundaes at midnight that we still talk about. This year SemiWiki had Dr. Paul McLellan, Dr. Eric Esteve, Daniel Payne, Don Dingee, Randy Smith, and… Read More

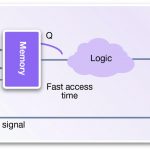

You can tune a piano, but you can’t tune a cache without help

Once upon a time, designing a product with a first generation SoC on board, we were trying to use two different I/O peripherals simultaneously. Seemed simple enough, but things just flat out didn’t work. After days spent on RTFM (re-reading the fine manual), we found ourselves at the absolute last resort: ask our FAE.

After about… Read More