Silent Data Corruption (SDC) represents a critical challenge in modern semiconductor design, particularly in high-performance computing environments like AI data centers. As highlighted in a collaborative presentation by Broadcom Inc. and Siemens EDA at the 2025 TSMC OIP event, SDC occurs when hardware defects cause erroneous… Read More

Tag: sta

New STA Features from Cadence

Static Timing Analysis (STA) has been an EDA tool category for many years now, yet with each new generation of smaller foundry process nodes come new physical effects that impact timing, requiring new analysis features to be added. For advanced process nodes, there are five different types of analysis that must be included when… Read More

Podcast EP105: Cadence STA Strategy and Capabilities, Today and Tomorrow with Brandon Bautz

Dan is joined by Brandon Bautz, senior group director of product management responsible for silicon signoff and verification product lines in the Cadence Digital & Signoff Group. Brandon has more than 20 years of experience in chip design and the EDA industry and has been at Cadence for over 10 years.

Dan explores the current… Read More

CEO Interview: Sivakumar P R of Maven Silicon

Sivakumar P R is the Founder and CEO of Maven Silicon. He is responsible for the company’s vision, overall strategy, business, and technology. He is also the Founder and CEO of Aceic Design Technologies.

Sivakumar is a seasoned engineering professional who has worked in various fields, including electrical engineering,… Read More

Webinar Replay – Insight into Creating a Common Testbench

These days the verification process starts right when the design process begins, and it keeps going well past the end of the design phase. Simulation is used extensively at every stage of design and can go a long way to help validate a design. However, for many types of designs, especially those that process complex data streams, … Read More

Xilinx on ANSYS Elastic Compute for Timing and EM/IR

I’m a fan of getting customer reality checks on advanced design technologies. This is not so much because vendors put the best possible spin on their product capabilities; of course they do (within reason), as does every other company aiming to stay in business. But application by customers on real designs often shows lower performance,… Read More

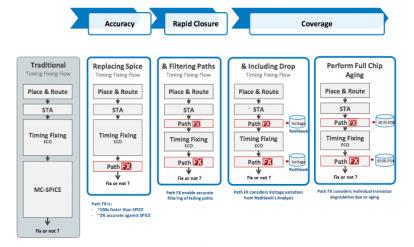

Peering Over the Timing Edge

I wrote recently about a yield problem which mobile vendors have been finding for devices built in advanced technologies. This was a performance issue (the devices worked fine at lower clock speeds), pointing to a discrepancy in some devices between predicted and observed timing. These were experienced design teams, using state… Read More

The Latest in Static Timing Analysis with Variation Modeling

In many ways, static timing analysis (STA) is more of an art than a science. Methodologists are faced with addressing complex phenomena that impact circuit delay — e.g., signal crosstalk, dynamic I*R supply voltage drop, temperature inversion, device aging effects, and especially (correlated and uncorrelated) process… Read More

In Low Voltage Timing, the Center Cannot Hold

When I started discussing this topic with Isadore Katz, I was struggling to find a simple way to explain what he was telling me – that delay and variance calculations in STA tools are wrong at low voltage because the average (the center) of a timing distribution shifts from where you think it is going to be. He told me that I’m not alone… Read More

FinFET: The Miller’s Tale

In Chaucer’s Canterbury Tales, the second of the tales told by the pilgrims is The Miller’s Tale. Since this is a family blog, I’ll leave you to research the tale yourself. But FinFETs hide another Miller’s Tale, due to Miller capacitance, sometimes called the Miller effect. This is significant since in FinFET designs Miller capacitance… Read More