The success of modern battery-powered products depends as much on useful operating time between charges as on functionality. FinFET process technologies overtook earlier planar CMOS in part because they significantly reduce leakage power. But they exacerbate dynamic power consumption thanks to increased pin capacitances.… Read More

Tag: soc

From Now to 2025 – Changes in Store for Hardware-Assisted Verification

Lauro Rizzatti recently interviewed Jean-Marie Brunet, vice president of product management and product engineering in the Scalable Verification Solution division at Siemens EDA, about why hardware-assisted verification is a must have for today’s semiconductor designs. A condensed version of their discussion is below.… Read More

Cliosoft and Microsoft to Collaborate on the RAMP Program

We have all heard of many advanced technological inventions and products from the defense sector that subsequently got commercialized. While most of the Defense Advanced Research Projects Agency (DARPA) projects are classified secrets, many military innovations have had great influence in the commercial sector in the fields… Read More

High-Speed Data Converters Accelerating Automotive and 5G Products

While the trend towards System-on-Chip (SoC) has been gathering momentum for quite some time, the primary driver has been integration of digital components, spurred by Moore’s law. Integrating more and more digital circuitry into a single chip has been consistently beneficial for performance, power, form factor and economic… Read More

Obtaining Early Analog Block Area Estimates

I’ve written before about Pulsic’s Animate Preview software, which is extremely helpful in completing placement in analog blocks so that they are ready for routing. Analog design automation has always been a tough proposition, but Animate Preview looks like a promising tool, with practical benefits. Obtaining DRC clean placement… Read More

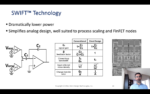

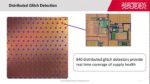

Analog Sensing Now Essential for Boosting SOC Performance

In today’s System-on-Chip (SOC), analog blocks are used in many places such as I/O cells for communication, PLLs for generating clocks, LDO’s for converting supply voltage to internal rail voltage, Sensors for qualifying external characteristics such as temperature, light, motion, etc. However new advanced designs now require… Read More

Webinar: Challenges in creating large High Performance Compute SoCs in advanced geometries

When we think about Compute and AI SoCs, we often focus on the huge numbers of calculations being carried out every second, and the ingenious IPs that are able to reach such high levels of performance. However, there also exists a significant challenge in keeping the vast quantities of data flowing around the chip which is solved … Read More

Automatic Generation of SoC Verification Testbench and Tests

Last month, I blogged about a webinar on embedded systems development presented by Agnisys CEO and founder Anupam Bakshi. I liked the way that he linked their various tools into a common flow that spans hardware, software, design, verification, validation, and documentation. Initially I was rather focused on the design aspects… Read More

Digital Design Technology Symposium!

Synopsys virtual events are high on my list for three reasons:

- They are very well organized and professionally

WEBINAR: Design Adaptive eFPGA IP

Since the start of PROMS, PLDs and FPGAs we have learned the importance of programmability in modern semiconductor design. Today we have eFPGAs for “design adaptive” embedded programmability and that is what this webinar is all about.

Several key points are discussed starting with the Law of Accelerating Returns as it applies… Read More