Once again with Synopsys and Arteris, the innovation is coming to solve an issue, faced by their potential customers: “In our research, we’ve found that almost half of project delays are caused by problems with the system architecture design and specification,” said Chris Rommel, vice president, embedded… Read More

Tag: soc

NoC for faster SoC integration

The need for Network-on-Chip (NoC) has appeared at the time where chip makers realized that they could really integrate a complete system on a single die to build a System-on-Chip (SoC). I was in charge of the development of a large IC, integrating different type of functions (Analog and Digital) to support advanced TV application.… Read More

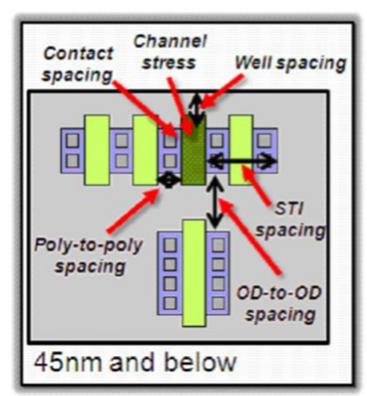

Layout for analog/mixed-signal nanometer ICs

Analog has always been difficult, a bit of a black art persuading a digital process to create well-behaved analog circuits, capacitors, resistors and all the rest. In the distant past, we would solve this by putting the analog on a separate chip, often in a non-leading-edge process. But modern SoCs integrate large amounts of digital… Read More

Intel Briefing: Tri-Gate Technology and Atom SoC

Sorry to disappoint but my 2 hours at the Intel RNB was a very positive experience. It is much more fun writing negative things about industry leaders because I enjoy the resulting hate mail and personal attacks, but the candor and transparency of the Intel guys won me over. They even asked ME questions which was a bit telling. I also… Read More

SOC Realization

There are some very interesting comments to the last entry on SoC Realization and how more and more chips are actually assembled out of IP. There was clearly a lot of discussion in this area at DAC, although most people (Atrenta being an exception) don’t use the term SoC Realization, presumably because it was originated by … Read More

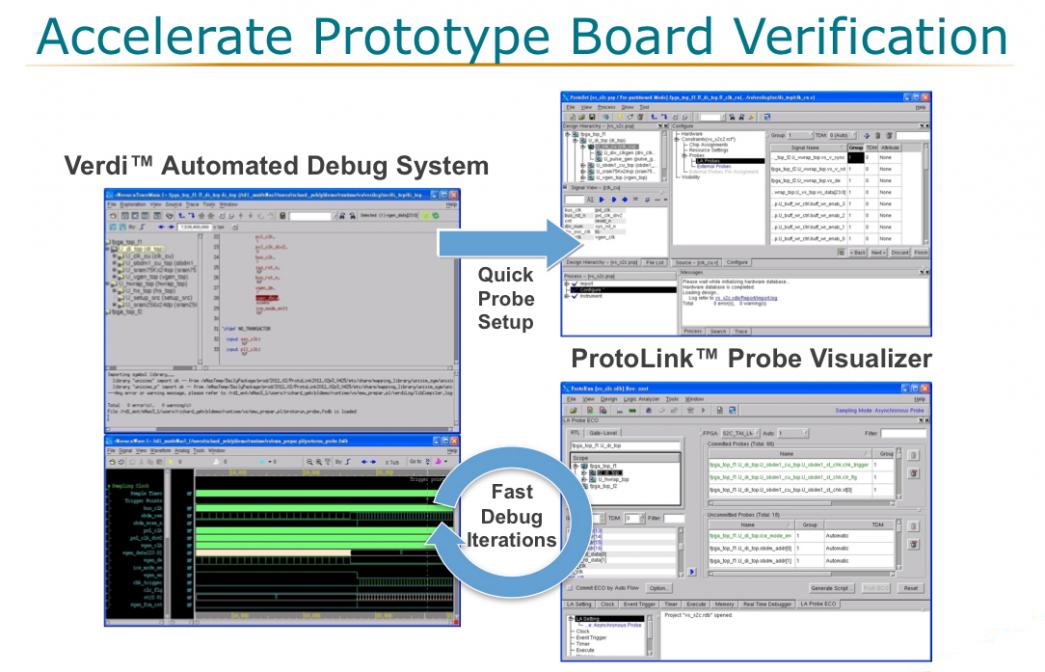

FPGA Prototypes Made Easy

FPGA-based prototype boards are a fast, cost-effective platform for SoC system validation but they are notoriously difficult to set up and to debug. There is a big upside, however, allowing early software integration and testing and thus finding bugs in both the software and the SoC earlier. This approach is much cheaper than … Read More

SOC Realization: How Chips Are Really Designed

If you just casually peruse most marketing presentations by EDA companies, you’d come to the conclusion most SoCs are designed from scratch, wrestlilng the monster to the ground with bare hands. But the reality is that most SoCs consist of perhaps 90% IP blocks (many of them memories). That still leaves the remaining 10% … Read More

ARM and GlobalFoundries

Although there has been always a strong relationship between ARM and GlobalFoundries, it is interesting to notice that Intel has helped to boost it and make it even stronger. Indeed when AMD renegotiated its x86 licensing deal with Intel in 2009, one of the most significant long-term changes was a marked reduction in how much of … Read More

Semiconductor IP would be nothing without VIP…

…but what is the weight of the Verification IP market?

If the IP market is a niche market (see: **) with revenue of about 1% of the overall semiconductor business, how could we qualify the VIP market? Ultra-niche market? But the verification of the IP integrated into the SoC is an essential piece of the engineering puzzle when you are… Read More

Clock Domain Crossing (CDC) Verification

Multiple, independent clocks are quintessential in SoCs and other complex ASICs today. In some cases, such as in large communications processors, clock domains may number in the hundreds. Clock domain crossings pose a growing challenge to chip designers, and constitute a major source of design errors–errors that can… Read More