Interesting to note; our cell phones today have more computing power than NASA had for the first landing on the moon. The insides of these mobile devices that we can’t live without are not like personal computers or even laptops with a traditional CPU (central processing unit) and a dozen other support chips. The brain, heart, and… Read More

Tag: soc

While you’re reading the SoC manual

There was a day, not too long ago, when a software developer could be intimate with a processor through understanding its register set. Before coding, developers would reach for a manual, digging through pages and pages of 1s and 0s with defined functions to find how to gain control over the processor and its capability. One bit set… Read More

The Total ARM Platform!

In the embedded world that drives much of today’s ASIC innovation, there is no bigger name than ARM. Not to enter the ARM vs. Intel fray, but it’s no exaggeration to say that ARM’s impact on SoCs is as great as Intel’s on the PC. Few cutting edge SoCs are coming to market that do not include some sort of embedded… Read More

TSMC: Production Proven Design Services Driving SoC Innovation!

One of the truisms of today’s disaggregated semiconductor design and manufacturing model is counter-intuitive to the do-it-yourself focus that is at the heart of every engineer. And yet, time and time again, success rewards those who understand that with today’s ever increasing complexity, it is difficult, if… Read More

Mind the Gap — Overcoming the processor-memory performance gap to unlock SoC performance

Remember the processor-memory gap— a situation where the processor is forced to stall while waiting for a memory operation to complete? This was largely a result of the high latency required for off chip memory accesses. Haven’t we solved that problem now with SoCs? SoCs are typically architected with their processors … Read More

Cadence Update 2012!

What’s new at Cadence? Quite a bit actually. I have always been a Cadence fan, I mean really, they gave birth to modern EDA. Unfortunately, Cadence really lost me during the Avant! legal action, the Mike Fister years, and EDA360. Recently, however, Cadence has made some big changes that will definitely get them back on my good side.… Read More

The Biggest EDA Company You’ve Never Heard Of

There’s this EDA company. They have over 100 tapeouts. They have a $28M in funding. They have 250 people. And you’ve never heard of them. Or at least I hadn’t.

They are ICScape. They started in 2005 with an investment from Acorn Campus Ventures and delivered their first product, ClockExplorer, in 2007 and their… Read More

Conquering the Big Data Challenges

Extrapolating the trends from last 20 years to the next ten suggests that we will be implementing a trillion transistors or more by 2020. At 20nm, with the chip sizes touching billions of transistors, the age old problem of how to implement a design in the most efficient manner remains unanswered. … Read More

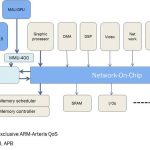

Virtual Prototype your SoC including FlexNoC

Designing larger than ever SoC, integrating multiple ARM’s Cortex-A15 and Cortex-A9 microprocessor cores as well as complexes IP functions like HDMI controller, DDR3 Memory controller, Ethernet, SATA or PCI Express controller are pushing designers to search for better price, performance and area tradeoffs and the SoC interconnect… Read More

Call for Papers: International Gathering for Application Developers!

SemiWiki would like to call you, your co-workers, and your company to participate at ERSA Conference in Las Vegas , July 16-19, 2012. I will be there and it would be a pleasure to work with you on this very important event!

ERSA, is Engineering of Reconfigurable Systems and Algorithms. Since this year, the emphasis will be on the commercial… Read More