Yes, it means complete hardware and software integration, debugging, verification, optimization of performance and power and all other operational aspects of an electronic system in semiconductor design. In modern SoCs, several IPs, RTL blocks, software modules, firmware and so on sit together on a single chip, hence making… Read More

Tag: soc

Cutting Debug Time of an SoC

The amount of time spent debugging an SoC dwarfs the actual design time, with many engineering teams saying that debug and verification takes about 7X the effort as the actual design work. So any automation to reduce the amount of time spent in debug and verification would directly impact the product schedule in a big way.

An example… Read More

Emerging Trend – Choose DRAM as per Your Design Need

Lately I was studying about new innovations in memory world such as ReRAM and Memristor. As DRAM (although it has become a commodity) has found its extensive use in mobile, PC, tablet and so on, that was an inclination too to know more about. While reviewing Cadence’s offering in memory subsystems, I came across this whitepaperwhich… Read More

Reliability sign-off has several aspects – One Solution

Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

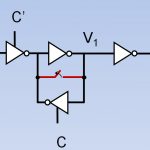

Ten Ways Your Synchronizer MTBF May Be Wrong

Estimating the MTBF of an SoC should always include an analysis of synchronizer reliability. Contemporary process nodes are introducing new challenges to the reliability of clock domain crossings so it is prudent to revisit how your simulation tool calculates a synchronizer’s MTBF. Let’s list the ten most common pitfalls.… Read More

Security Needs in On-Chip Networks

I remember during my first ten years as a software developer, I used many different computers such as IBM mainframes, Apollo and Sun workstations, and VAX computers. During that time I also bought my first home computer, a Macintosh. I didn’t of course think of this at the time, but the one thing they all had in common was that they did… Read More

Innovation + Thoughtful Management = Productive Expansion

After looking at various aspects of this company, to sum up, I couldn’t find any better statement than this; thoughtful management here is actually leadership with passion which achieves tangible results. This reflects in the methodology of doing things in this company which has given it a place among top EDA companies in a span… Read More

Accelerating SoC Simulation Times

There never seems to be enough time in a SoC project to simulate all of the cycles and tests that you want to run, so any technique to accelerate each run is welcomed. You can just wait for your software-based RTL simulator to finish running, or you can consider using a hardware-based accelerator approach. I learned more about one such… Read More

Don’t Shoot Yourself in the Foot With Timing Exceptions

Timing exceptions are ways of guiding design tools, primarily synthesis and static timing analysis (STA), but these days also place & route and perhaps other tools. Most paths in a design go from one register to the next register. Both registers are on the same clock, and the design needs to ensure that the signal can make it from… Read More

Xilinx picks another winner…

Just as important as block RAMs, IO and DSP48’s is what interconnect or fabric is going to be used when considering SoC FPGA designs. I think Xilinx has found the winning combination. What is paramount to the new SoC FPGA methodologies is not only the challenge of moving huge amounts of data around; we are now to consider data… Read More