Talk to the members of a digital design team and you will always find two types of users. One who likes using the GUI while working on his design and the other who is passionate about using scripts and the command line options. This is akin to the two camps of users who either love either good old Vi/Vim or the ever versatile Emacs editor.… Read More

Tag: soc

Who is Driving This Car Anyway?

My Lyft driver in San Jose thought his Hyundai had “autopilot,” alluding I suspected, to Tesla Motors’ feature of the same name which has placed that company at the forefront of driving automation development and the focal point of fatal crash investigations. Before either of us got hurt I gently disabused my driver of his dangerous… Read More

Free webinar – Accelerating data processing with FPGA fabrics and NoCs

FPGAs have always been a great way to add performance to a system. They are capable of parallel processing and have the added bonus of reprogramability. Achronix has helped boost their utility by offering on-chip embedded FPGA fabric for integration into SoCs. This has had the effect of boosting data rates through these systems… Read More

WEBINAR: Generating and Measuring IP Security Threat Levels For Your SoCs

IPs have an attack surface that indicates how they can be compromised in real world scenarios. Some portions of the attack surfaces are well known, others are discovered during analysis, testing or out in the field. SoCs that use large collections of IPs need a systematic and reliable way to determine the various security vulnerabilities… Read More

Webinar – AI/ML SoC Memory and Interconnect IP Perspectives

For decades development work on Artificial Intelligence (AI) and Machine Learning (ML) was done on traditional CPUs and memory configurations. Now that we are in the “hockey stick” upturn in deployment of AI and ML, the search is on for the most efficient types of processing architectures. The result is a wave of development for… Read More

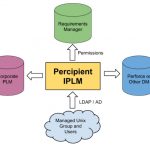

IP Lifecycle Management and Permissions

My first professional experience with computers and file permissions was at Intel in the late 1970s, where we used big iron IBM mainframes located far away in another state, and each user could edit their own files along with browse shared files from co-workers in the same department. I saw this same file permission concept when … Read More

Are the 100 Most Promising AI Start-ups Prototyping?

I came across a report on the 100 most promising AI start-ups. The report claimed that CBInsights had “selected the 100 most promising AI start-ups from a pool of 3K+ companies based on several factors …” Wait, what … 3K+ companies!?!? This was a stunning reminder of the sheer magnitude of what is shaping up to be a veritable tsunami… Read More

SiP is the new SoC @ 56thDAC

The emergence of 3D packaging technology has been accompanied by the term “more than Moore”, to reflect the increase in areal circuit density at a rate that exceeds the traditional IC scaling pace associated with Moore’s Law. At the recent Design Automation Conference in Las Vegas, numerous exhibits on the vendor floor presented… Read More

Automotive Design and Virtual Prototyping

The entire history of EDA software tools has enabled engineers to design ICs and SoCs using virtual prototyping, so most of us in the industry are familiar with the idea of modeling and simulating something as complex as an IC before actually starting the manufacturing process. In a complex system like an automobile there are a lot… Read More

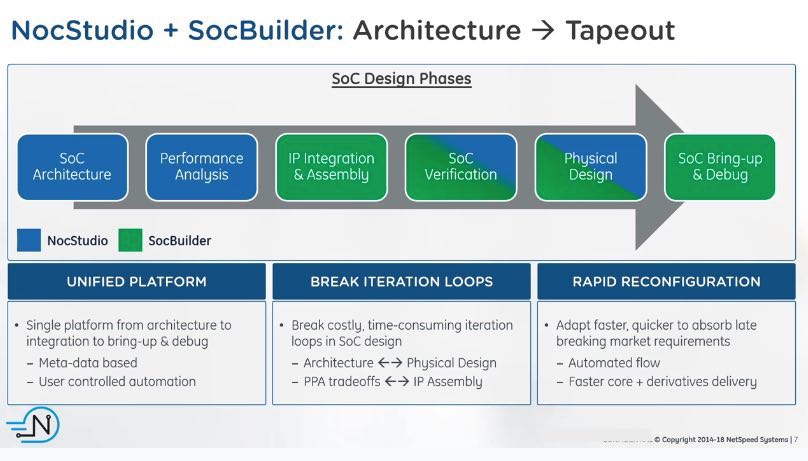

Webinar: NetSpeed is about to change the way SOCs are designed

A large part of the effort in designing SOCs has shifted to the integration of their constituent IP blocks. Many IP blocks used in SOCs come as ready to use components and the real work has become making them work together. Network on Chip (NoC) has been a huge help in this task, handling the interconnections between blocks and planning… Read More