A large part of the effort in designing SOCs has shifted to the integration of their constituent IP blocks. Many IP blocks used in SOCs come as ready to use components and the real work has become making them work together. Network on Chip (NoC) has been a huge help in this task, handling the interconnections between blocks and planning for anticipated traffic. NoCs have evolved quite a bit, becoming more like full blown networks, offering features like QoS, traffic management, cache coherency, high reliability and true layered networking protocols. NetSpeed, a leading provider of NoC technology, is using its foundation technology and a number of innovations to expand their offering to address a much larger part of the job of integrating IP blocks to build an SOC.

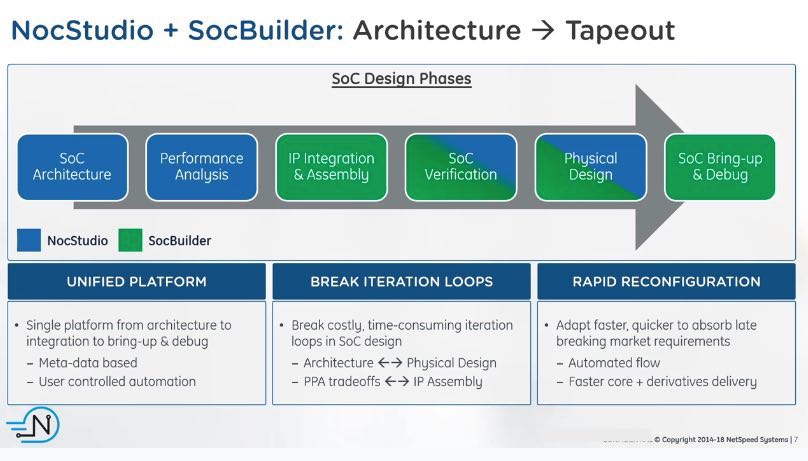

NetSpeed’s NocStudio already helps with making architecture decisions and analyzing performance. It also helps with some aspects of SOC verification and physical design. Their new offering, SocBuilder goes much further by handling IP integration and assembly. Additionally, it compliments NocStudio in the areas of SOC verification and physical design. Even more interestingly it provides support for SOC bring-up and debug. Because SocBuilder and NocStudio share a single platform, they share metadata and can be controlled and automated as a single system.

One of SocBuilder’s key features is the use of reference designs and an extensive IP catalog. Information gleaned from the reference designs and protocol information from the IP catalog are used by machine learning, and advanced data analytics and visualization to assist the design process. Because much of the work during SOC design is related to protocol related issues, this is a ripe area for improved analysis and automation. SocBuilder works with IP descriptions in IPXACT and has extensions for additional metadata for IP. NetSpeed is working with a large number of partners to ensure good coverage of popular IP in their catalog.

With the large array of metadata and IP information available to SocBuilder, it can help with all aspects of physical design, including clock/reset/power, trace/debug/telemetry, MMU/security, and interrupts. These chassis related aspects of the design can be vexing, so having tools to guide the process can be critical to meeting quality goals and deadlines. SocBuilder uses industry standard LEF/DEF during floor planning. SocBuilder assists with connectivity and address map design as well.

After floor planning, system simulations can be run in SocBuilder to ensure performance, power and functional safety goals are met. There is visual feedback for a wide variety of system performance parameters such as power and thermal, etc. The final design is then run through extensive LINT checks that covers protocols, power, connections, performance, etc. System level deadlock checks are also included in SocBuilder.

The outputs are comprehensive. SocBuilder provides SystemC, RTL for the design description. DEF, SDC and scripts are output for the physical design. Test benches are also generated. SocBuilder helps with the essential task of software design too. It produces C models, reference documentation and a programmer’s guide. PPA metrics are also output.

There is an upcoming webinar to acquaint SOC designers with the features and to go into more depth regarding how it works. The Webinar will be on Tuesday August 28[SUP]th[/SUP] at 8AM Pacific Time and registration information is available on the NetSpeed website.I did not dwell much on the machine learning aspect, but this is a reminder that machine learning is in the process of transforming design. Companies that have experience with ML in design and that are expanding its use will certainly be able to make big leaps in enhancing designer productivity.

Share this post via:

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!