When most people hear the term PDF, they immediately think of a PDF file, a universal, platform-independent way to share electronic documents.

There is, however, another PDF that many outside the semiconductor industry may not be familiar with. And this PDF actually predates the PDF file format. It is short for PDF Solutions, … Read More

By Jason Liu, RFIC-GPT Inc.

Radio frequency integrated circuits (RFICs) have become increasingly critical in modern electronic systems, driven by the rapid growth of wireless communication technologies (5G/6G), the Internet of Things (IoT), and advanced radar systems. With the desire for lower power consumption, higher… Read More

DVCON U.S. 2026by Admin on 08-27-2025 at 10:06 pm

DVCon is the premier conference on the application of languages, tools, and methodologies for the design and verification of electronic systems and integrated circuits. The focus of the conference is the usage of specialized design and verification languages such as SystemVerilog, Verilog, VHDL, PSS, SystemC and e, as well… Read More

I mentioned in an earlier blog that multiple presentations at DVCon 2025 went all-in on AI-assisted design and verification. The presentation was one such example, looking very much at top-down AI-expert application of agentic flows to design and verification. AlphaDesign is a new startup out of UC Santa Barbara headed by William… Read More

Meet with proteanTecs at DAC. Explore our full set of health and performance monitoring solutions. We’ll be showcasing our latest products and solutions, and we’d love to connect while you’re there. Visit booth #2417 to explore our health and performance monitoring solutions.

Also – Don’t miss out… Read More

Without data, there is no computing field to talk about, no technology world to awe at and not much of a semiconductor industry to work in. There is no argument that data is the foundational piece for everything, has been to date and will continue to be. While processing an application’s input data is essential to serve the intended… Read More

In sports, we’re all familiar with how even a team with the best individual players for every role needs to be coordinated as a team to win a championship. In healthcare, a patient is better served with a well-trained primary physician to coordinate with the various medical specialists. The field of semiconductors involves a series… Read More

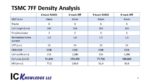

I have written a lot of articles looking at leading edge processes and comparing the process density. One comment I often get are that the process density numbers I present do not correlate with the actual transistor density on released products. A lot of people want to draw conclusions an Intel’s processes versus TSMC’s processes… Read More

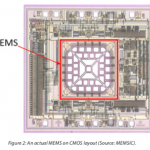

I mentioned a while back that I’m really getting into the role that sensors play in our new hyper-connected world – in the IoT, intelligent cars, homes, cities, industry, utilities, medicine, agriculture, etc, etc. If we can think of a way to sense it and connect it, someone is probably already doing it. But there’s more to … Read More

I enjoy learning and writing about new technologies closely connected to our personal and working lives (the kind you could explain to your Mom or a neighbor). So naturally I’m interested in AI, communication and security as applied to the home automation, transportation, virtual, augmented and mixed reality, industry and so… Read More