A large part of the effort in designing SOCs has shifted to the integration of their constituent IP blocks. Many IP blocks used in SOCs come as ready to use components and the real work has become making them work together. Network on Chip (NoC) has been a huge help in this task, handling the interconnections between blocks and planning… Read More

Tag: nocstudio

Software Defined Networks (on Chip) – NetSpeed Systems and UltraSoC Team Up to Use Embedded Analytics to Enable Next Generation SoCs

NetSpeed Systems is known for their network-on-chip (NoC) IP that enables complex heterogeneous SoC architectures. NetSpeed IP supports both non-coherent and coherent memory and I/O schemes as well as configurable, customized last level cache optimization through their Orion, Gemini and Pegasus IP respectively. They are… Read More

NetSpeed’s Pegasus Last-Level Cache IP Improves SoC Performance and Reduces Latency

Memory is always a critical resource for a System-on-Chip (SoC) design. It seems like designers are always wanting more memory, and the memory they have is never fast enough to keep up with the processors, especially when using multi-core processors and GPUs. To complicate matters, today’s SoC architectures tend to share memory… Read More

NetSpeed Taking a Ride with Autonomous Automobiles

The push for autonomous automobiles continues at a rapid pace. Last week a new conference was held in Santa Clara, CA by the Linley Group focused on Autonomous Hardware. The group included presentations from GLOBAL FOUNDRIES, Synopsys, NetSpeed Systems, Arteris, EMBC, Cadence, CEVA, ARM and Trilumina covering ADAS and autonomous… Read More

Executive Interview: Joe Rowlands, Chief Architect at NetSpeed Systems

Joe has devoted his career to understanding and designing cache coherent systems and has been granted over 95 patents on the subject. For the past four years, he has been Chief Architect at NetSpeed, a developer of network-on-chip SoC interconnect.… Read More

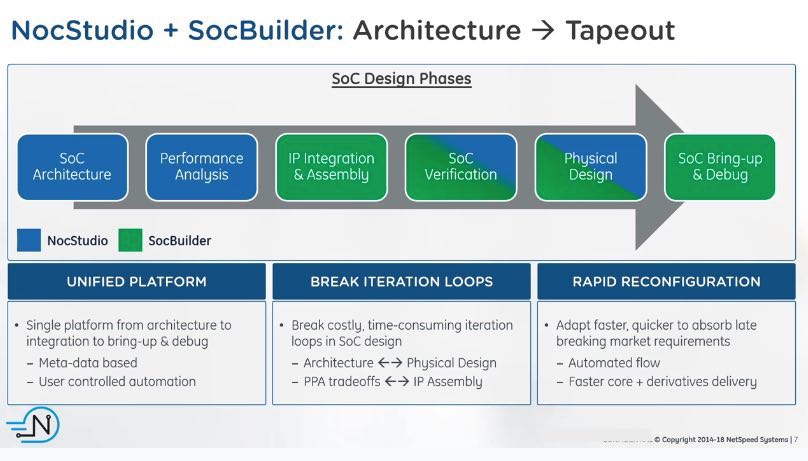

NetSpeed Bridges the Gap Between Architecture and Implementation

This is part II of an article covering NetSpeed’s network-on-chip (NoC) offerings. This article dives a little deeper into what a NoC is and how NetSpeed’s network synthesis tool, NocStudio, helps system architects optimize a NoC for their system-on-a-chip (SoC) design.

Traditionally IC designers have used proprietary buses,… Read More

Can you really address the Automotive market with AP designed for smartphone?

If you remember, when TI decided to exit the booming wireless segment in 2012, the company decided to re-focus their application processor product line (OMAP) initially developed for smartphone “to a broader market including industrial clients like carmakers”. Being a TI employee in the 90’s in south of France, where TI has started… Read More

How to Build a Deadlock-Free Multi-cores SoC?

We will precisely explain the meaning of deadlock in a modern, complex multi-core SoC. First, let’s take a look at the crash of the Air France 296, when a brand new Airbus A320 crashed during a demo flight on June 26, 1988. This Airbus 320, the first plane being completely automated, thanks to the FADEC flight system, was running a demo… Read More

Why Gemini 2.0 is tailored for tomorrow’ SoC designs?

You probably have seen many times this graphic showing that the number of IP blocks has exploded, going from a few dozens in SoC designed in 65 nm to 120 if not more for last generation SoC targeting 16FF or 10FF. This graphic is very good at synthesizing the raw IP count, but it doesn’t tell you about another strong trend: more agents … Read More

How to Overcome NoC Validation Multiple Challenges?

NetSpeed has developed NocStudio, a front end optimization design tool helping architects to create SoC architecture bridging the gap with the back end, floor planning and place and route. At the chip level, NocStudio generates a cache-coherent Network-on-Chip (NoC) allowing interconnecting the various CPU, GPU or Acceleration… Read More