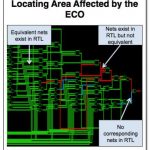

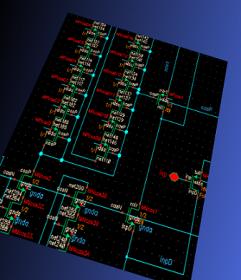

One of the most challenging stages in an SoC design is achieving timing closure. Actually design closure is perhaps a better term since everything needs to come together such as clock tree, power nets, power budget and so on. Changes made to the design are known as ECOs (which stands for engineering change orders, a term that comes… Read More

Tag: soc

Missed #50DAC? See Aldec Verification Sessions Online

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

SoC Sign-off, Real Intent at DAC

Monday morning at DAC I met with Real Intent to get an update on their SoC sign-off tools:

- Dr. Prakash Narain, President and CEO

- Graham Bell, Sr. Dir. Mktg.

Years ago Prakash was at IBM the only two years that they attended DAC, in an attempt to offer their internal EDA tools to the EDA marketplace. Graham worked at Nassda marketing the… Read More

A bird told me the EDPS Monterey Conference was a great success

The 20th annual Electronic Design Process Symposium (EDPS) held April 18-19 at the Monterey Beach Hotel in Monterey California was an unqualified success. I know this because a bird (seagull?) sitting on the window sill of the conference room was so captivated by the fascinating insight provided by a number of luminaries that … Read More

FPGAS – The New Single Board Computers?

I have always felt that FPGAs have been the red haired step child of Silicon Valley. Software weenies have hated them, they are mysterious and take too long to route. Even though they can be massively parallel and the most deterministic piece of silicon you can buy besides a million dollar ASIC, the GPU steals their glory, for now. … Read More

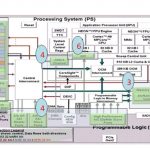

Ivo Bolsens’ Keynote on the All-Programmable SoC

Ivo Bolsens, the CTO of Xilinx, is giving the opening keynote at the Electronic Design Process Symposium (EDPS) in Monterey on Thursday and Friday this coming week. The title of his keynote is The All Programmable SoC – At the Heart of Next Generation Embedded Systems. He covers a lot of ground but the core of his presentation… Read More

Schematic Migration Across Foundries and Processes

A dedicated schematic migration tool can save weeks of effort and allow companies to explore new foundry opportunities. Unfortunately moving analog and mixed signal design data between foundries and processes is a complex business. While engineers would rather spend their days creating new circuits, many spend time translating… Read More

Ensuring timing of Custom Designs with large embedded memories – A big burden has solution!

In 1990s when designs were small, I was seeing design and EDA community struggling to improve upon huge time taken to verify the circuits, specifically with Spice and the like. I was myself working on developing tool for transistor level static timing analysis (STA) mainly to gain on time (eliminating the need of exhaustive set … Read More

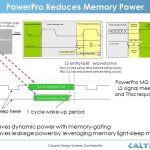

Dynamic/Leakage Power Reduction in Memories

Embedded memories have an important impact on power. SoCs that integrate multiple functions on a single silicon die are at the heart of many electronic devices. As process geometries have scaled, design teams have used more and more of the additional silicon real estate available to integrate embedded memories that serve as scratch-pads,… Read More

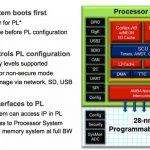

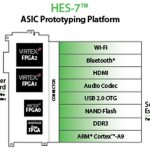

Zynq out of the box, in FPGA-based prototyping

Roaming around the hall at ARM TechCon 2012 left me with eight things of note, but one of the larger ideas showing up everywhere is the Xilinx Zynq. Designers are enthralled with the idea of a dual-core ARM Cortex-A9 closely coupled with programmable logic.… Read More