In today’s SoC world where multiple analog and digital blocks along with IPs at different levels of abstractions are placed together on a single chip, debugging at all levels becomes quite difficult and clumsy. While one is working at the top level and needs to investigate a particular connection at an intermediate hierarchical… Read More

Tag: soc

What’s Behind Carbon System Exchange – How Will it Scale?

Earlier this year, when I was looking at Carbon’spast year performance which provided record breaking revenue with whopping jump in bookings, one thing was certain that Carbon Performance Analysis Kits (CPAKs) would drive major growth in future, not only for Carbon, but also for the semiconductor industry. It will initiate … Read More

A Comprehensive Power Analysis Solution for SoC+Package

Since power has become a critical factor in semiconductor chip design, the stress is towards decreasing supply voltage to reduce power consumption. However, the threshold voltage to switch devices cannot go down beyond a certain limit and these results in an extremely narrow margin for noise between the two. And that gets further… Read More

Design Collaboration across Multiple Sites

Any SoC or IC design project, whether implemented at the same design site or multiple sites requires some data management tools to manage things such as a central data repository, revision management of files, etc., for effective co-ordination of work among different team members. Given the challenge of meeting the shrinking… Read More

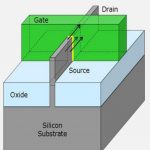

FinFETs for your Next SoC

Planar CMOS processes have been offered for decades now, and all the way down through the 28nm node it has been riding the benefits of Moore’s Law. A few years back we started hearing from Intel about TriGate (aka FinFET) starting at the 22nm node as a way to use a more 3D processing approach for transistors instead of planar CMOS.… Read More

Automatic RTL Restructuring: A Need Rather Than Convenience

In the semiconductor design industry, most of the designs are created and optimized at the RTL level, mainly through home grown scripts or manual methods. As there can be several iterations in optimizing the hierarchy for physical implementation, it’s too late to do the hierarchical optimizations after reaching the floor plan… Read More

IoT will depend on FPGAs

The IoT (Internet of Things) creates an ambivalence within me. Part of me hates computers and being connected, the other is currently working on a boiler controller that even adaptively predicts and senses when the next wood load is needed and alerts the wife. Yup pray for her. I really use FPGAs and CPLDs around the farm and I am slowly… Read More

NoCs for system-level power management

Most of the buzz on network-on-chip is around simplifying and scaling interconnect, especially in multicore SoCs where AMBA buses and crossbars run into issues as more and more cores enter a design. Designers may want to explore how NoCs can help with a more power-aware approach.… Read More

When is a Million-Year MTBF Too Short?

The reliability metric, Mean Time Between Failures (MTBF), is often misunderstood. Use of an MTBF metric generally assumes a random failure process, one that is very infrequent and has no memory of past failures. Such failure modes can occur in System-on-Chip (SoC) designs and include radiation effects, synchronizer malfunctions… Read More

Winds of Change in the Custom Chip Market

The most interesting part of the semiconductor market for me has always been the Custom Chip sector – the FPGA, ASIC and SoC companies where I have spent my entire career. These three segments provide an excellent barometer of the overall state of financial health and technological innovation for the entire High Tech industry, … Read More