In June of 2013 Edward Snowden copied and leaked classified information from the National Security Agency (NSA). His actions exposed numerous surveillance programs that many governments around the world reacted to, including China. In September of 2013 China Vice Premier Ma Kai declared semiconductors a key sector for the … Read More

Tag: soc

NetSpeed Leverages Machine Learning for Automotive IC End-to-End QoS Solutions

A couple of weeks back I wrote an article about the use of machine learning and deep neural networks in self-driving cars. Now I find that machine learning is also being applied to help build advanced end-to-end QoS (quality of service) solutions for the automotive IC market. With the advent of self-driving cars comes requirements… Read More

Performance Analysis for ARM Based SOC’s

ARM estimates that many SOC’s designed today have over 200 IP components. This statistic comes from a recent white paper ARM published addressing the topic of system performance analysis. This number is only going to go up. According the ARM this creates a huge challenge in ensuring the system is designed with adequate performance… Read More

Bringing the Semiconductor IP Community Together!

Next week is the first REUSE Semiconductor IP Tradeshow and Conference at the Computer History Museum in Silicon Valley. The presentation abstracts are up now and there are a few I want to highlight as they are companies that we work with on SemiWiki.… Read More

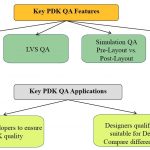

Is That PDK Safe to Use Yet?

In our semiconductor ecosystem we have foundries on one side supplying all of that amazing silicon technology, and IC designers on the other side that take their system ideas then go implement them in a SoC using a specific foundry. The required interface between foundry and chip designers has been the Process Design Kit (PDK), … Read More

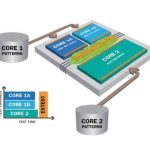

DFT Approaches for Giga-gate SoC Designs

In the early days of IC design there were arguments against using any extra transistors or gates for testability purposes, because that would be adding extra silicon area which in turn would drive up the costs of the chip and product. Today we are older and wiser, realizing that there are product pricing benefits to quickly test each… Read More

SOC Design Techniques that Enable Autonomous Vehicles

Robots – we have all been waiting for them since we were young. We watched Star Wars, or in the case of the slightly longer-lived of us, we watched Forbidden Planet or Lost in Space. We knew that our future robot friends would be able to move around and interact with their environment. What we did not foresee long ago was that instead of… Read More

SoC FPGAs for IoT Edge Computing

One of the reasons for the explosive growth of IoT is that embedded devices with networking capabilities and sensor interfaces are cheap enough to deploy them at a plethora of locations.

However, network bandwidth is limited. Not only that, but also, the latency of the network can be of seconds or minutes. By the time the sensor data… Read More

The Perfect Wearable SoC…?

Power is Everything

During Apollo 13 after the oxygen tank in the service module exploded forcing the crew to use the lunar module as a life boat to get back home, John Aaron – an incredibly gifted NASA engineer who was tasked with getting the Apollo 13 crew back home safely – flatly stated “Power is everything…we’ve… Read More

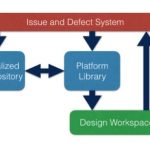

5 Reasons Why Platform Based Design Can Help Your Next SoC

Semiconductor design IP and verification IP have been around for decades, but just because your company has lots of IP doesn’t mean that you’re getting all of the benefits of a design reuse methodology. Maybe your business has encountered some of the following issues: