The continued innovation and widespread adoption of connected devices — the internet of things (IoT) — has resulted in a vast range of conveniences that improve our lives every day. At the same time, the ubiquity of IoT devices, which market watchers estimate to be in the tens of billions, also makes it more attractive to bad actors… Read More

Tag: soc design

Prototyping with the Latest and Greatest Xilinx FPGAs

I was reading the S2C press release announcing their new FPGA prototyping platform based on the Xilinx UltraScale+ VU19P FPGA, and how the new FPGA will accelerate billion gate FPGA prototyping, and I was struck by the stunning implications of this announcement. Not that billion gate SoC designs can now be prototyped with FPGAs,… Read More

Embedded Systems Development Flow

Earlier this year. as part of my coverage of the virtual Design Automation Conference (DAC), I interviewed Agnisys CEO and founder Anupam Bakshi. He talked about the new products they introduced at the show and filled me in on the history of the company and his own background. Recently, Anupam presented the webinar “System Development… Read More

Why IP Designers Don’t Like Surprises!

If it’s your job to get a SoC design through synthesis, timing/power closure and final verification, the last thing you need are surprises in new versions of the IP blocks that are integrated into the design. If your IP supplier sends a new version, the best possible scenario is that this is only a small incremental change from… Read More

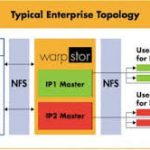

WEBINAR: Lightspeed Data Sync – Design Workspace Problems Solved!

With every process node and every SOC design, engineering and IT teams are experiencing an unprecedented data explosion. User workspaces routinely exceed 10’s of GB and sometimes even 100’s of GB. Regression runs, characterization runs, design and debug of workspaces, building verification environments – all of these… Read More

Webinar: VLSI Design Methodology Development (new text)

Daniel Nenni was gracious enough to encourage me to conduct a brief webinar describing a new reference text, recently published by Prentice-Hall, part of the Semiwiki Webinar Series.

VLSI DESIGN Methodology Development Webiner Replay

Background

I was motivated to write the text to provide college students with a broad background… Read More

Early IP Block Error Detection is Critical!

The rising complexity of modern SoC designs, as enabled by progressing manufacturing technology, leads to an increasing validation challenge as the only way to manage complexity increase is by re-using more pre-designed IP blocks. These IP-blocks are provided by various suppliers such as a foundry partner, internal design… Read More

The Complexity of Block-Level Placement @ 56thDAC

The recent Design Automation Conference in Las Vegas was an indication of how the electronics industry is evolving. In its formative years, DAC was focused on the fundamental algorithms emerging from academic research and industrial R&D, that enabled the continuation of the Moore’s Law complexity curve. (Indeed, the… Read More

The Changing Face of IP Management

Aristotle once said “The whole is greater than the sum of its parts”. The notion of synergism echoes the importance of leveraging design IPs to the maximum extent with the rest of the system under development, in order to ensure a successful SoC design outcome in a shorter development cycle.

SoC design cost and entry point

For over… Read More

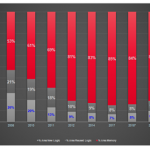

Webinar: The Emergence of FPGA Prototyping for ASIC and SoC Design

One of the more interesting markets that I cover is FPGA Prototyping. Interesting because it is fast growing ($150-250M) and interesting because it is all about design starts and design starts are the lifeblood of the semiconductor industry.

If you are interested in FPGA prototyping you might want to start with the 30+ S2C Inc blogs… Read More