You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The arrival of optical computing has been predicted every year for the last fifteen years. As with any other technology backed by prolific research, lofty goals get dialed back as problems are identified. What emerges first is a set of use cases where the technology fits with practical, realizable implementations.

When it comes… Read More

On the first two chapters of this Tutorial we started with a simple LFSR module and added a test bench. Then, on chapters three and four we upgraded our module with some features and learned to export the test bench data to files.

… Read More

In the first part of this tutorialwe started with a simple implementation of an LFSR block (Chapter 1) and its test bench (Chapter 2). Let’s make our code look a bit more professional.

… Read More

In this tutorial we will see how to design a VHDL block. We will start with a very simple block and we will gradually add features to it. We will also simulate it and test its output with Matlab. Over the process we will see:

… Read More

Teams buy HDL simulation for best bang for the buck. Teams buy hardware emulation for the speed. We’ve talked previously about SCE-MI transactors as a standardized vehicle to connect the two approaches to get the benefits of both in an accelerated testbench – what else should be accounted for?… Read More

Designers tend to put tons of energy into pre-silicon verification of SoCs, with millions of dollars on the line if a piece of silicon fails due to a design flaw. Are programmable logic designers, particularly those working with an SoC such as the Xilinx Zynq, flirting with danger by not putting enough effort into verification?… Read More

Several companies have attacked the QoS problem in SoC design, and what is emerging from that conversation is the best approach may be several approaches combined in a hybrid QoS solution. At the recent Linley Group Mobile Conference, NetSpeed Systems outlined just such a solution with an unexpected plot twist in synthesis.

The… Read More

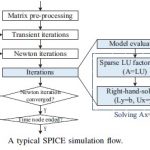

SPICE simulation is the workhorse tool for custom circuit timing validation and electrical analysis. As the complexity of blocks and macros has increased in advanced process nodes — especially with post-layout extraction parasitic elements annotated to the circuit netlist — the model size and simulation throughput… Read More

If your team is building large, complex designs that require millions of clock cycles to fully verify, you need both simulation and emulation.

Using emulation with simulation accelerates performance for dramatically reduced run times.… Read More

UVM has become a preferred environment for functional verification. Fundamentally, it is a host based software simulation. Is there a way to capture the benefits of UVM with hardware acceleration on an FPGA-based prototyping system? In an upcoming webinar, Doulos CTO John Aynsley answers this with a resounding yes.… Read More