Apparently this event is now being postponed until sometime later in the year. Stay tuned

We spend a lot of our time with our heads down in the technical details and when we look up at what we think is the big picture, it’s usually just a little bit bigger, often no more than a justification for immediate product directions. So wouldn’t… Read More

Tag: power

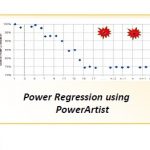

How to nail your PPA tradeoffs

How do you ensure your design has been optimized for power, performance, and area? I posed this question to Mentor’s Group Director of Marketing, Sudhakar Jilla and product specialist Mark Le. They said that finding the PPA sweet spot is still often done by trial and error – basically serial experiments with various input parameters… Read More

Galaxy S7 and the Ongoing Charging Guessing Game

In the back-and-forth competition between Samsung and Apple, the Galaxy S7 certainly seems to have notched a few wins over the iPhone 6S. Most reviewers feel the Samsung camera is noticeably superior and the overall look and feel is on a par with or better than the Apple product. I want to focus on just one area where Samsung differs… Read More

Who will provide data center Soc of the future, Intel or Qualcomm ?

Intel has been incredibly successful by designing high performance server SoC to address the data center market segment, and the chance to see the company loosing large market share is pretty low, at least in the short term. Now, if we look at the really long term, 2030 or even 2040, like did the Semiconductor Industry Association… Read More

A Brief History of Defacto Technologies

In early 2000s, semiconductor design at RTL level was gaining momentum. The idea was to process more design steps such as insertion of test and other design structures upfront at the RTL level. The design optimization and verification were to be done at the RTL level to reduce long iterations through gate level design because changes… Read More

5 Verification Challenges of IoT Solved by Emulation

Software-centric Emulation environment takes the forefront in modern SoC verification. As more and more devices are IoT enabled, the SoCs have to make special provisions to factor many things including communication, power usage, and network switching, and so on. Also, the demand for an SoC (specifically for smartphone which… Read More

How to Gain Low-Power at High-Performance

In a world of smart devices, high performance is required in order to address several specific needs such as intelligent and immediate data processing for IoT applications, instant response from mobile devices, highly interactive user interfaces, and so on. Most of these devices are battery operated and hence require lower … Read More

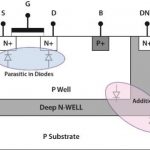

28nm FD-SOI: A Unique Sweet Spot Poised to Grow

I have been silently watching STMicroelectronics pursuing FD-SOI technology since quite a few years. FinFET was anyway getting more attention in the semiconductor industry because of several factors involved. But from a technology as well as economic perspective there are many plus points with FD-SOI. I remember my debate,… Read More

Together At Last—Combining Netlist and Layout Data for Power-Aware Verification

The market demanded that gadgets it loves become ever more conscious of their power consumption, and chip designers responded with an array of clever techniques to cut IC power use. Unsurprisingly, these new techniques added to the complexity of IC verification. When you’re verifying a design that has 100+ separate power domains,… Read More

A Complete Simulation Platform for Mobile Systems

If we take an insight into the semiconductor industry, we can easily find that mobile systems are the main drivers of this industry. The Smartphone business has remained at the top since a good number of years. Although the Smartphone sales growth has started showing a sign of stagnation, it is still a main contributor with a solid… Read More