You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

20nm SoC Designby Paul McLellan on 08-25-2011 at 12:48 amCategories: Uncategorized

There are a large number of challenges at 20nm that didn’t exist at 45nm or even 32nm.

The biggest issues are in the lithography area. Until now it has been possible to make a reticle using advanced reticle enhacement technology (RET) decoration and have it print. Amazing when you think that at 45nm we are making 45nm features… Read More

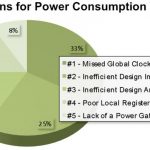

Traditionally, David Letterman style, we should really have the top 10 reasons for wasting power in semiconductor design, but here are the five big ones.

Starting with reason #5: Lack of a power gating strategy

Leakage power is a huge proportion of total power and the only way to save leakage power (apart from low leakage cells when… Read More

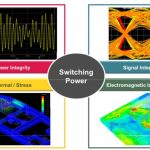

ANSYS/Apacheby Paul McLellan on 08-13-2011 at 2:43 pmCategories: Ansys, Inc., EDA

Last week I met with Andrew Yang, erstwhile CEO of Apache Design Systems and now formally President of Apache Design Inc, a wholly owned subsidiary of ANSYS. The merger formally closed at the start of the month. Within ANSYS Apache is positioned as Chip-aware System-level Engineering Simulation. ANSYS is pretty much completely… Read More

The Totem webinar will be at 11am on Tuesday 2nd August. This session will be conducted by Karan Sahni, Senior Applications Engineer at Apache Design Solutions. Karan has been with Apache since 2008, supporting the Redhawk, Totem, Sentinel product lines. He received his MS in Electrical Engineering from the Syracuse University… Read More

At DAC 2011 in San Diego, Apache gave many product presentations. Of course not everyone could make DAC or could make all the presentations in which they were interested. So from mid-July until mid-August these presentations will be given as webinars. Details, and links for registration, are here on the Apache website.

The seminars… Read More

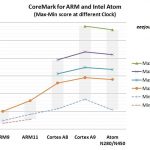

This blog was posted 10 months ago, and the comments have made it much more interesting! Don’t miss the various comments at the back. Also feel free to let us know if you think the status, in this ARM vs Intel “war” has changed a lot since March 2011. Do you really think Intel has catch up with ARM in the mobile industry?… Read More