At the recent DesignCon 2020 in Santa Clara, Cadence introduced a new product, Sigrity Aurora. You won’t find a press release about this announcement. Rather, Brad Griffin, product management group director at Cadence, presented Sigrity Aurora in the theater at the Cadence booth. This one caught my eye and deserves some discussion.… Read More

Tag: power integrity

Mentor Automating Design Compliance with Power-Aware Simulation HyperLynx and Xpedition Flow

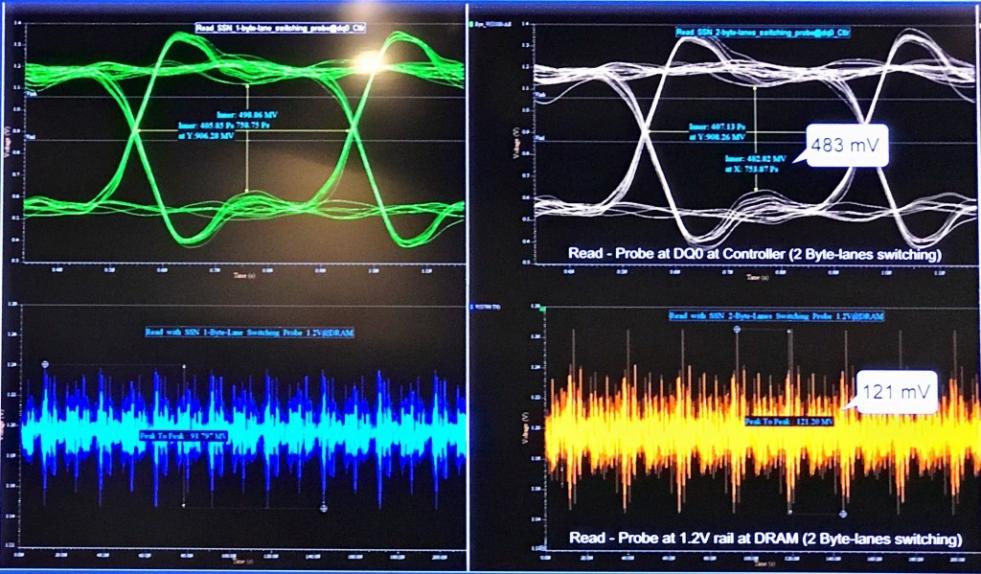

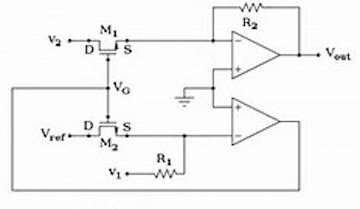

High-speed design requires addressing signal integrity (SI) and power integrity (PI) challenges. Power integrity has a frequency component. The Power Distribution Network (PDN) in designs has 2 different purposes: providing power to the chip, and acting as a power plane reference for transmission-line like propagating … Read More

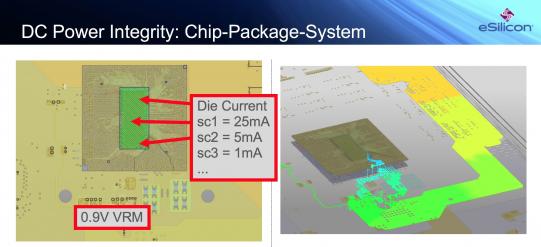

Chip, Package, System Analysis – A User View

While I missed ANSYS (and indeed everyone else) at DAC this year, I was able to attend the ANSYS Innovation Conference last week at the Santa Clara Convention Center. My primary purpose for being there was to listen to a talk by eSilicon which I’ll get to shortly, but before that I sat through a very interesting presentation on the growing… Read More

A True Signoff for 7nm and Beyond

The Tale of Three Metrics

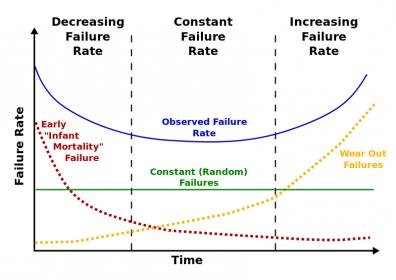

Meeting PPA (Performance, Power and Area) target is key to a successful design tapeout. These mainstream QoR (Quality of Results) metrics are rather empirical yet inter-correlated and have been expanded to be linked with other metrics such as yield, cost and reliability. While the recent CPU performance… Read More

Webinar: Multiphysics Reliability Signoff for Next-Generation Automotive Electronics Systems

In case you missed the TSMC event, ANSYS and TSMC are going to reprise a very important topic – signing-off reliability for ADAS and semi-autonomous /autonomous systems. This topic hasn’t had a lot of media attention amid the glamor and glitz of what might be possible in driverless cars. But it now seems like the cold light of real … Read More

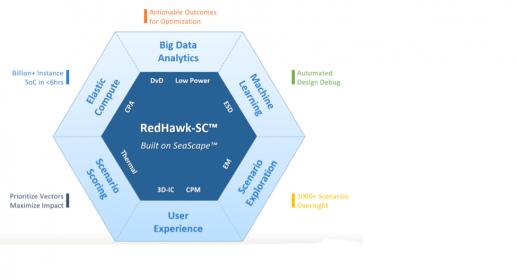

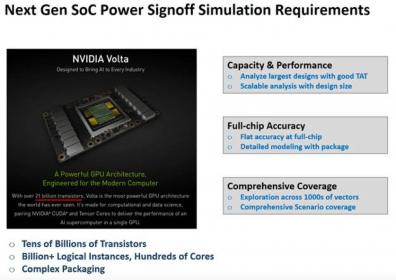

Big Data Analytics and Power Signoff at NVIDIA

While it’s interesting to hear a tool-vendor’s point of view on the capabilities of their product, it’s always more compelling to hear a customer/user point of view, especially when that customer is NVIDIA, a company known for making monster chips.

A quick recap on the concept. At 7nm, operating voltages are getting much closer… Read More

Webinar: High-Capacity Power Signoff Using Big Data

Want to know how NVIDIA signs off on power integrity and reliability on mega-chips? Read on.

PPA over-design has repercussions in increased product cost and potential missed schedules with no guarantee of product success. Advanced SoCs pack more functionality and performance resulting in higher power density, but traditional… Read More

Webinars: Bumper Pack of AMS Webinars from ANSYS

Power integrity and reliability are just as important for AMS designs as they are for digital designs. Ansys is offering a series of five webinars on this topic, under a heading they call ANSYS in ACTION, a bi-weekly demo series from ANSYS in which an application engineer shows you how simulation can address common applications.… Read More

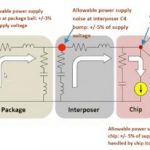

Power Integrity from 3DIC to Board

The semiconductor industry has built decades of success on hyper-integration to increase functionality and performance while also reducing system cost. But the standard way to do this, to jam more and more functionality onto a single die, breaks down when some of the functions you want to integrate are built in different processes.… Read More

Big Data and Power Integrity: Drilling Down

I’ve written before about how Ansys applies big data analytics and elastic compute in support of power integrity and other types of analysis. A good example of the need follows this reasoning: Advanced designs today require advanced semiconductor processes – 16nm and below. Designs at these processes run at low voltages, much… Read More