You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

We’ve been saying for a while that it looks like there is a resurgence in design starts for ASICs targeting the IoT. A recent webinar featuring speakers from ARM and Open Silicon (and moderated by Daniel Nenni) affirms this trend, and provides some insight on how these designs may differ from typical microcontrollers.

One of my first… Read More

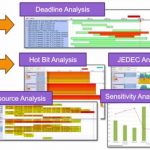

In our previous post on SoC memory resource planning, we shared 4 goals for a solution: optimize utilization and QoS, balance traffic across consumers and channels, eliminate performance loss from ordering dependencies, and analyze and understand tradeoffs. Let’s look at details on how Sonics is achieving this.… Read More

The classical problem every MBA student studies is manufacturing resource planning (MRP II). It quickly illustrates that at the system level, good throughput is not necessarily the result of combining fast individual tasks when shared bottlenecks and order dependency are involved. Modern SoC architecture, particularly … Read More

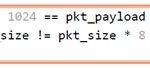

For the latest incremental improvements to its Riviera-PRO functional verification platform, Aldec has turned to streamlining random constraint performance. The new Riviera-PRO 2016.02 release also is now fully supported on Windows 10 and adds a new debugger tool.… Read More

Sales says this next IoT project is going to be huge. Engineering isn’t so sure. Marketing says we should pilot it to find out. If it were just software, it might not be such a problem, but with hardware comes investment tradeoffs. Without guaranteed volumes of millions of units, are ASICs a realistic option to hit aggressive size,… Read More

What we think of as a “baseband processor” for cellular networks is often comprised of multiple cores. Anecdotes suggest to handle the different signal processing requirements for 2G, 3G, and 4G networks, some SoC designs use three different DSPs plus a control processor such as an ARM core. That’s nuts. What is the point of having… Read More

When most people talk about the IoT, it is usually all about wearables-this and low-power-that – because everyone is chasing the next huge consumer post-mobile device market. Mobile devices have provided the model. The smartphone is the on-ramp to the IoT for most consumers, with Bluetooth, Wi-Fi, and LTE, and maybe a dozen or … Read More

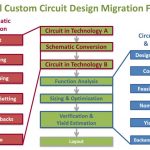

Reusing design IP is crucial for competitiveness. The need for reuse occurs with new designs on the same process node as the original design, new designs at the same node but using a different PDK or foundry, or designs on a different process node – usually smaller. However, achieving effective IP reuse has always been a challenge.… Read More

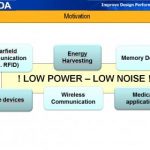

We have been hearing about low power for a long time. Fortunately, low power chip operation has come about through a large number of innovations. Key among these is clock gating, frequency and voltage scaling, managing leakage with lower threshold voltage, HKMG, and many other techniques. But we are entering the age of ultra low… Read More

In optimizing SoC design for performance, there is so much focus on how fast a CPU core is, or a GPU core, or peripherals, or even the efficiency of the chip-level interconnect. Most designers also understand selecting high performance memory at a cost sweet spot, and optimizing physical layout to clock it as fast as possible within… Read More