You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

We know by now that clock speeds aren’t everything when it comes to measuring the goodness of a processor. Performance has direct ties to pipeline and interconnect details, power factors into considerations of usability, and the unspoken terms of yield drive cost.

My curiosity kicked in when I looked at the recent press release… Read More

Big processors get all the love, it seems. It’s natural, since they are highly complex beasts and need a lot of care and feeding in the EDA and fab cycle. But the law of large numbers is starting to shift energy in the direction of optimizing microcontrollers.

I mulled the math in my head for a while. In a world with 7 billion people and … Read More

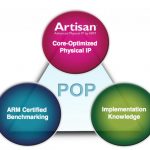

Just in time for TSMC’s technology symposium (tomorrow) ARM have announced a whole portfolio of new Processor Optimization Packs (POPs) for TSMC 40nm and 28nm. For most people, me included, my first question was ‘What is a POP?’

A POP is three things:

- physical IP

- certified benchmarking

- implementation knowledge

…

Read More