Last week, Intel announced its second-quarter financial results which easily beat the analysts’ consensus expectations by a handsome margin. Yet the stock price plummeted by over 16% right after the earnings call with management. Seven analysts downgraded the stock to a sell and the common theme on all the downgrades was that… Read More

Tag: moore’s law

Contact Resistance: The Silent Device Scaling Barrier

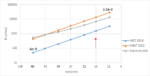

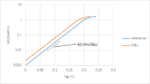

Moore’s Law has been about device density, specifically transistor density, increasing every certain number of years. Although cost is the most easily grasped advantage, there are two other benefits: higher performance (speed) and reduced power. When these benefits are compromised, they can also pose a scaling limitation.

MOSFET Gate Length Scaling Limit at Reduced Threshold Voltages

As transistor dimensions shrink to follow Moore’s Law, the functionality of the gate used to switch on or off the current is actually being degraded by the short channel effect (SCE) [1-5]. Moreover, the simultaneous reduction of voltage aggravates the degradation, as will be discussed below.

A Practical Lower Limit of… Read More

ASML A Scenario More Lumpy While Demand and Tech Remain Solid Despite Covid Delays

Covid issues create “lumpy” quarters due to delays

Orders & demand remain solid and strong

2020 Year financials intact so far but ignore Qtrs

Taking prudent actions- no buybacks or guidance

As expected, Covid impacts both shipments & supply chain, ignore the near term lumpiness…

ASML reported revenues… Read More

Short vs Long Term Covid19 Impact

-Short term Covid19 impact is primarily logistics related

-Longer term impact is more systemic/demand driven

-Impact will wind through supply chain over several qtrs

-Other issues, such as trade, remain an overhang

Short term versus long term in the semiconductor industry

The stocks declines over the last months seem to indicate… Read More

Talking Sense With Moortec – The Future Of Embedded Monitoring Part 2

The rate of product development is facing very real challenges as the pace of silicon technology evolution begins to slow. Today, we are squeezing the most out of transistor physics, which is essentially derived from 60-year-old CMOS technology. To maintain the pace of Moore’s law, it is predicted that in 2030 we will need transistors… Read More

Intersection of Technologies

Monitoring brain activities and translating the signals into commands to control devices is truly a ‘Cool Idea’. Nurio is the latest winner of Protolabs’ Cool Idea award – a $250k grant towards manufacturing services to rapid prototype and accelerate the product to the market. (Click here to learn

TSMC – Solid Q3 Beat Guide- 5G Driver – Big Capex Bump – Flawless Execution

TSMC puts up solid QTR, Capex increase for 5NM and capacity increase, 5G/mobile remains driver- HPC good 7NM, 27% of revs- Very nice margins!

In line quarter-Good guide

TSMC reported revenues of $9.4B and EPS of $0.62 , more or less in line with expectations, perhaps a touch below ” whisper” expectations which had been… Read More

IEDM 2019 to Highlight Innovative Devices for an Era of Connected Intelligence

The IEEE International Electron Devices Meeting is in my opinion the leading technology conference to understand the current state-of-the-art in semiconductor process technology. Held each year in early December in San Francisco it is a must attend conference for anyone following technology development. The following is… Read More

Chapter 3 – Moore’s Law is Unconstitutional!

(Adapted from a presentation first given under this title in 1989 and subsequently expanded in presentations over a period of nearly thirty years)

In 1965, Gordon Moore, then R&D Manager for Fairchild Semiconductor, published a paper in “Electronics” magazine predicting the trend for semiconductors in the next ten years. … Read More