You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

A Brief History of Mentor Graphicsby Beth Martin on 08-20-2012 at 11:00 pmCategories: EDA, Siemens EDA

In 1981, Pac-Man was sweeping the nation, the first space shuttle launched, and a small group of engineers in Oregon started not only a new company (Mentor Graphics), but an entirely new industry, electronic design automation (EDA).

Mentor founders Tom Bruggere, Gerry Langeler, and Dave Moffenbeier left Tektronix with a great… Read More

There was a day, not too long ago, when a software developer could be intimate with a processor through understanding its register set. Before coding, developers would reach for a manual, digging through pages and pages of 1s and 0s with defined functions to find how to gain control over the processor and its capability. One bit set… Read More

A Brief History of EDAby Daniel Nenni on 08-05-2012 at 6:00 pmCategories: EDA

Electronic Design Automation, or more affectionately known as EDA, is a relatively young $5B industry with a very colorful upbringing, one that I have experienced firsthand, I’m very grateful for, and is an honor to write about. Today EDA employs an estimated 27,000 people! There is a nice EDA Wikipedia page which can be found here… Read More

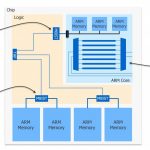

Benjamin Franklin, “I didn’t fail the test, I just found 100 ways to do it wrong.” I was reminded of this line during a joint Mentor-ARM seminar yesterday about testing ARM cores and memories. The complexity of testing modern SoC designs at advanced nodes, with multiple integrated ARM cores and other IP, opens up plenty of room for… Read More

If you are involved in testing memory or logic of ARM-based designs, you’ll want to attend this free seminar on July 17, 2012 in Santa Clara. Mentor Graphics and ARM have a long standing partnership, and have optimized the Mentor test products (a.k.a Tessent) for the ARM processors and memory IP.

The lunch seminar runs from 10:30-1:00… Read More

IC Test Sessions at SEMICON West 2012by Beth Martin on 07-02-2012 at 1:43 pmCategories: EDA, Siemens EDA

SEMICON West is coming up this July 10-12 at the Moscone Center in San Francisco. It covers a broad swath of the microelectronics supply chain, but I was particularly interested in the test sessions. Here are two that I recommend.

“The Value of Test for Semiconductor Yield Learning” on Tuesday, July 10, at 1:30p. The… Read More

The days following a major conference like DAC are a good time to reflect on the overall health and vibrancy of the electronic design automation (EDA) industry. I’ve been in EDA for 21 years and built two successful startups, and over the last couple of years, have witnessed some decline in both new talent and in venture investment… Read More

I got an email from Mentor Embedded this morning about a webinar on Implementing a GENIVI-compliant System. I have to admit I had no idea what GENIVI is, which surprised me. I spent several years working in the embedded space and so I usually have at least a 50,000 foot view of most things going on there. One reason for my ignorance is … Read More

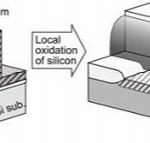

Have you ever heard of a Super Pillar Transistor? It’s one of many emerging 3D transistor types, like Intel’s popular FinFET device.

In the race to continuously improve MOS transistors, these new 3D transistor structures pose challenges to the established IC extraction tool flows.

Foundries have to provide an Effective… Read More

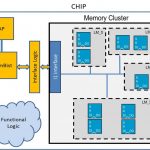

Smaller IC nodes bring new challenges to the art of IC layout for AMS designs, like Layout Dependent Effects (LDE). If your custom IC design flow looks like the diagram below then you’re in for many time-consuming iterations because where you place each transistor will impact the actual Vt and Idsat values, which are now a … Read More