Ever since the birth of the semiconductor industry, advances have always been at a fast pace. The complexity of SoCs have grown along the way, driven by the demanding computational and communication needs of various market applications. Over the last decade, the growth in complexity has accelerated at unforeseen rates, fueled… Read More

Tag: interconnect

SEMICON West – Applied Materials Selective Gap Fill Announcement

At SEMICON West, Applied Materials announced a new selective gap fill tool to address the growing resistance issues in interconnect at small dimensions. I had the opportunity to discuss this new tool and the applications for it with Zhebo Chen global product manager in the Metal Deposition Products group at Applied Materials.… Read More

Webinar – AI/ML SoC Memory and Interconnect IP Perspectives

For decades development work on Artificial Intelligence (AI) and Machine Learning (ML) was done on traditional CPUs and memory configurations. Now that we are in the “hockey stick” upturn in deployment of AI and ML, the search is on for the most efficient types of processing architectures. The result is a wave of development for… Read More

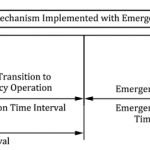

What are SOTIF and Fail-Operational and Does This Affect You?

Standards committees, the military and governmental organizations are drawn to acronyms as moths are drawn to a flame, though few of them seem overly concerned with the elegance or memorability of these handles. One such example is SOTIF – Safety of the Intended Function – more formally known as ISO/PAS 21448. This is a follow-on… Read More

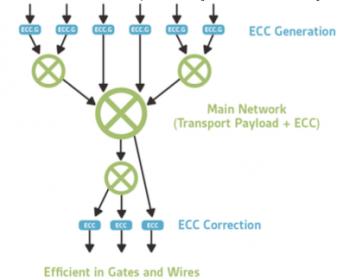

Supporting ASIL-D Through Your Network on Chip

The ISO 26262 standard defines four Automotive Safety Integrity Levels (ASILs), from A to D, technically measures of risk rather than safety mechanisms, of which ASIL-D is the highest. ASIL-D represents a failure potentially causing severe or fatal injury in a reasonably common situation over which the driver has little control.… Read More

SEMICON West – Advanced Interconnect Challenges

At SEMICON West I attended the imec technology forum where Zsolt Tokei presented “How to Solve the BEOL RC Dilemma” and the SEMICON Economics of Density Scaling session where Larry Clevenger of IBM presented “Interconnect Scaling Strategic for Advanced Semiconductor Nodes”. I also had the opportunity… Read More

Automation for managed system-of-systems design

Anybody who has done any bus & board system design knows the problem. Merchant boards typically have standardized pinouts (after years of haggling in standards organizations) for the backplane bus, and a group of user-defined pins for daughtercard I/O. Homegrown systems usually have a just-as-carefully defined proprietary… Read More

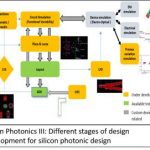

Electrical-Optical Design, A Bridge to Terabitsia

If you don’t get the tongue in cheek reference of the title, you probably don’t have children who liked to watch Disney movies. All four of my daughters loved Disney and so, I am forever shaped by the Wonderful World of Disney. In 2007 Disney adapted to the screen a novel called, ‘A Bridge to Terabithia’, in which two adolescents escape… Read More

New CoreLink IP ties in mobile GPU coherently

A mobile GPU is an expensive piece of SoC real estate in terms of footprint and power consumption, but critical to meeting user experience demands. GPU IP tuned for OpenGL ES is now a staple in high performance mobile devices, rendering polygons with shading and texture compression at impressive speeds.

Creative minds in the desktop… Read More

SEMI SMC: Atoms Still Don’t Scale

Last Tuesday was the SEMI’s annual Strategic Materials Conference (SMC). The opening keynotes were given by Gary Patton, the CTO of GlobalFoundries, and Mark Thirsk, Managing Partner of Linx Consulting. This year it was held in the Computer History Museum (which always makes the commute interesting since you have to fight… Read More