One of my favorite traditions at the Design Automation Conference is the Synopsys foundry events (the videos are now available). I learned a long time ago that the foundries are the foundation of the fabless semiconductor ecosystem and your relationships with the foundries can make or break you, absolutely. I also appreciate … Read More

Tag: globalfoundries

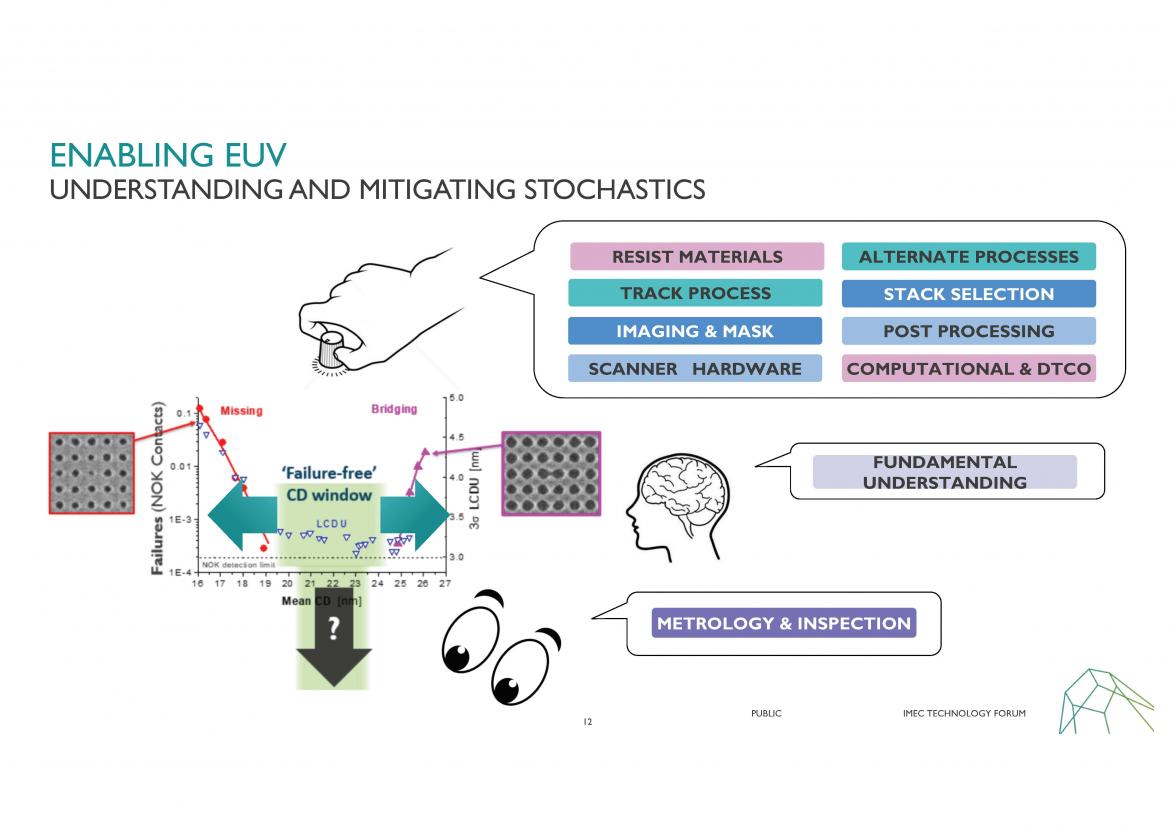

SEMICON West – Leading Edge Lithography and EUV

At SEMICON West I attended the imec technology forum, multiple Tech Spot presentations and conducted a number of interviews relevant to advanced lithography and EUV. In this article I will summarize what I learned plus make some comments on the outlook for EUV.… Read More

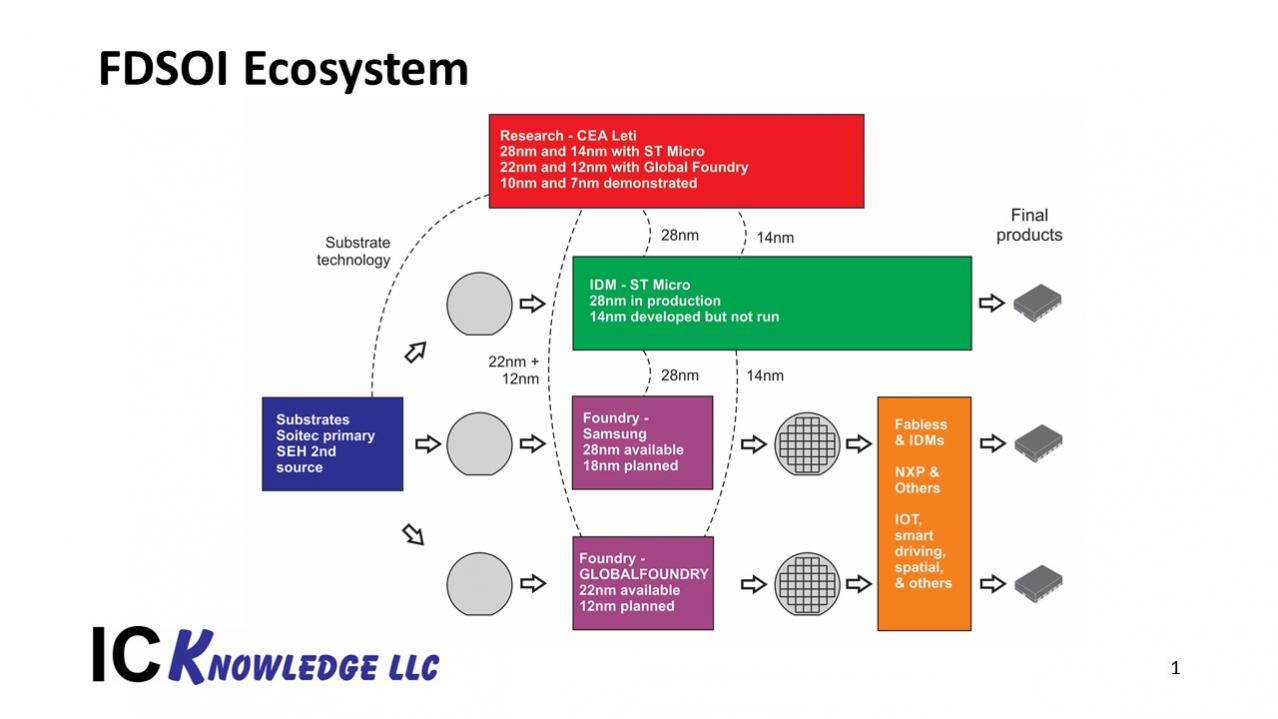

FDSOI Status and Roadmap

FDSOI is gaining traction in the market place. At their foundry forum in May, Samsung announced they have 17 FDSOI products in high volume manufacturing (you can read Tom Dilliger’s write up of the Samsung Foundry Forum here). At SEMICON West in July, GLOBALFOUNDRIES (GF) announced FDSOI design wins worth $2 billion dollars in … Read More

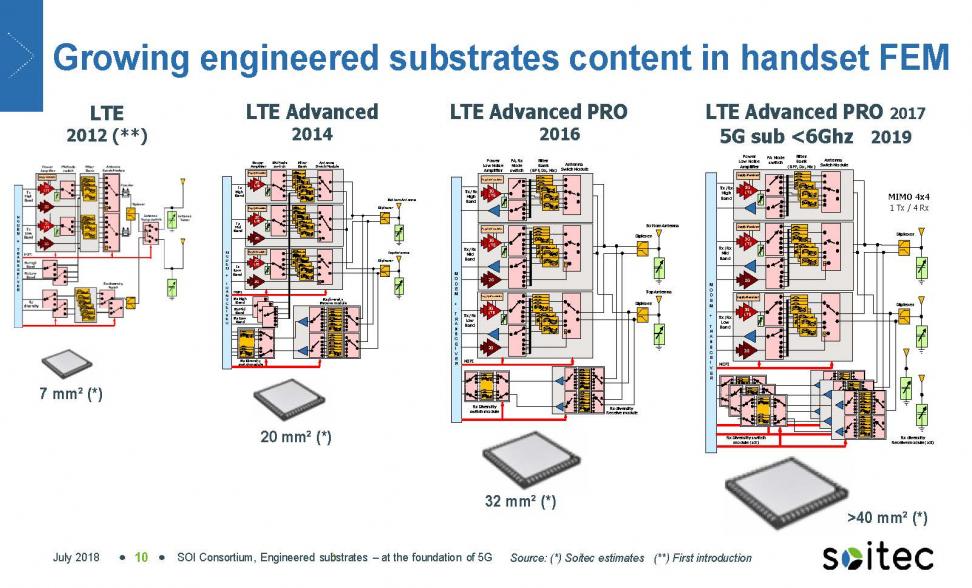

SEMICON West – Soitec is becoming a key enabler

A variety of growing and emerging segments of the semiconductor industry rely on Silicon-On-Insulator (SOI) wafers. Soitec is the primary source for SOI wafers particularly on 300mm. On Tuesday at SEMICON I got to sit down with Bernard Aspar, Soitec’s Executive Vice President, Communication & Power BU and Christophe… Read More

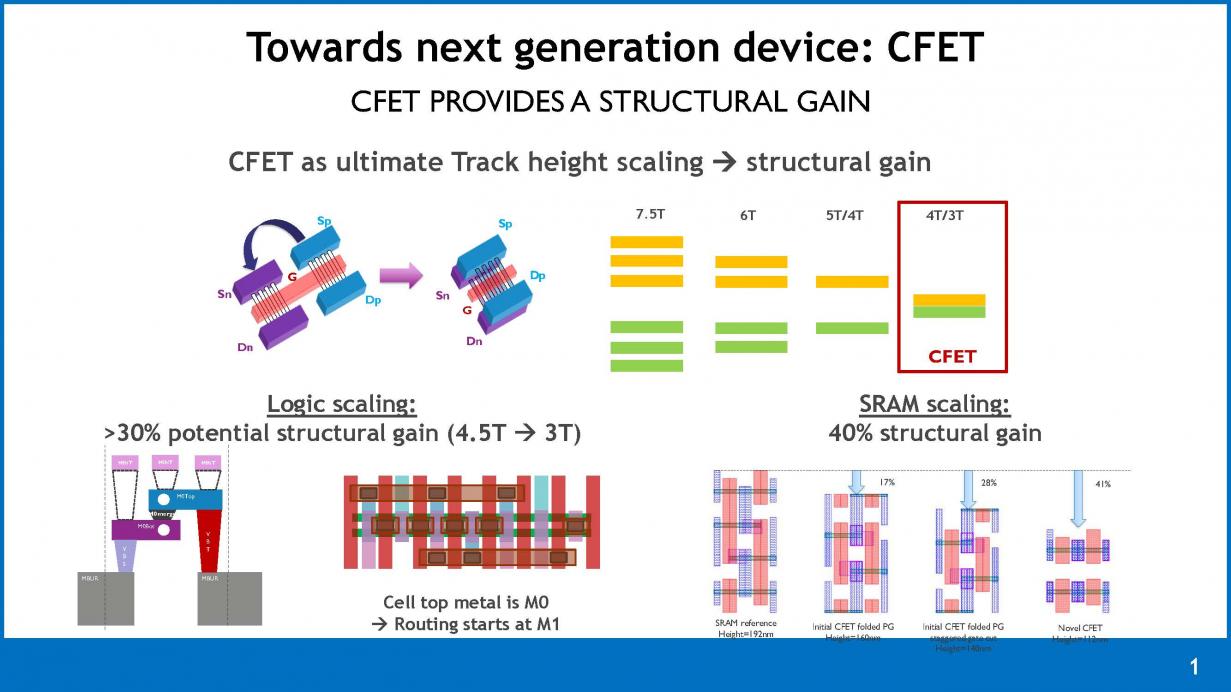

VLSIT Conference – imec on CFETs

The 2018 VLSI Technology conference was held in Hawaii in June and is one of the premier conferences covering integrated circuit process technology and circuit design. The Complementary FET (CFET) is an emerging option to continue logic scaling into the next decade. At the conference imec, GLOBALFOUNDRIES, Tokyo Electron and… Read More

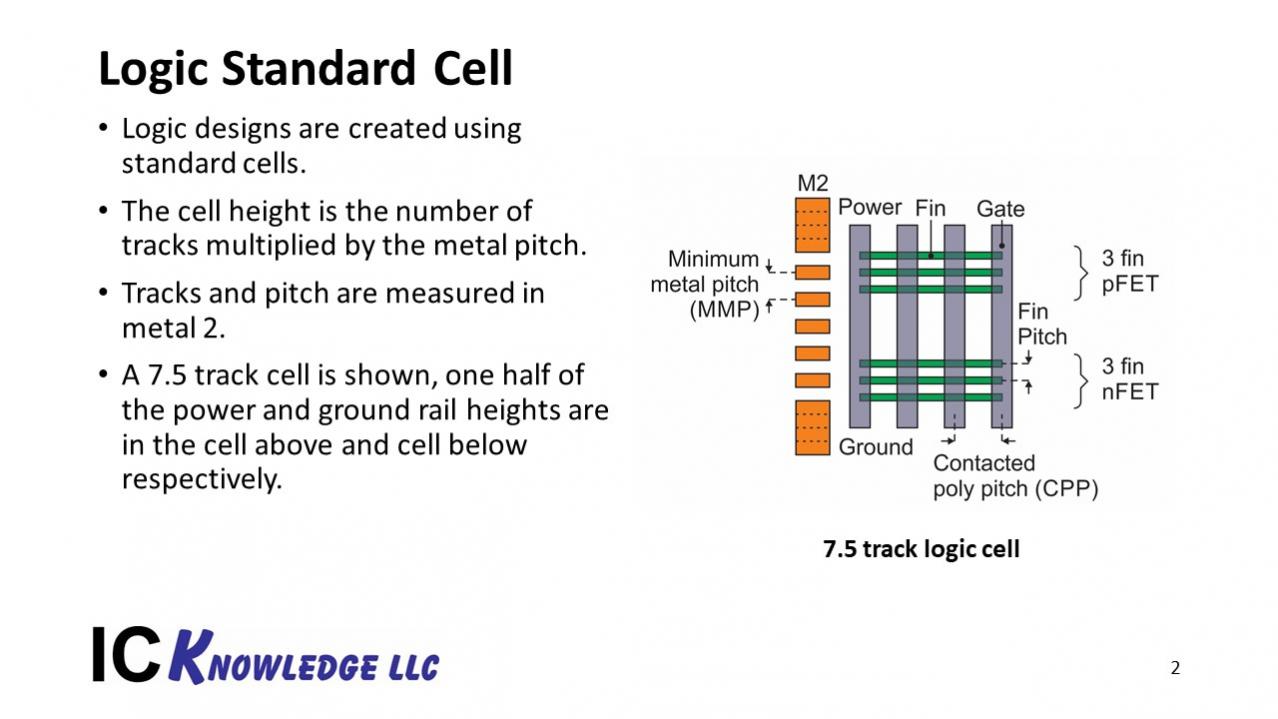

7nm, 5nm and 3nm Logic, current and projected processes

There has been a lot of new information available about the leading-edge logic processes lately. Papers from IEDM in December 2017, VLSIT this month, the TSMC and Samsung Foundry forums, etc. have all filled in a lot of information. In this article I will summarize what is currently known.… Read More

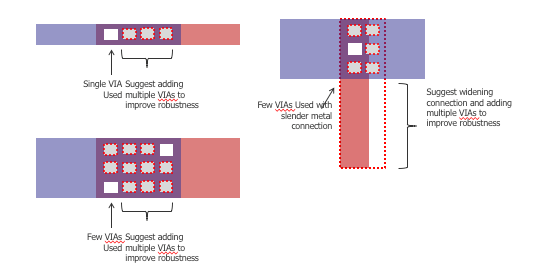

Foundry Partnership Simplifies Design for Reliability

This builds on a couple of topics I have covered for quite a while from an analysis point of view – integrity and reliability. The power distribution network and some other networks like clock trees are particularly susceptible to both IR-drop and electromigration (EM) problems. The first can lead to intermittent timing failures,… Read More

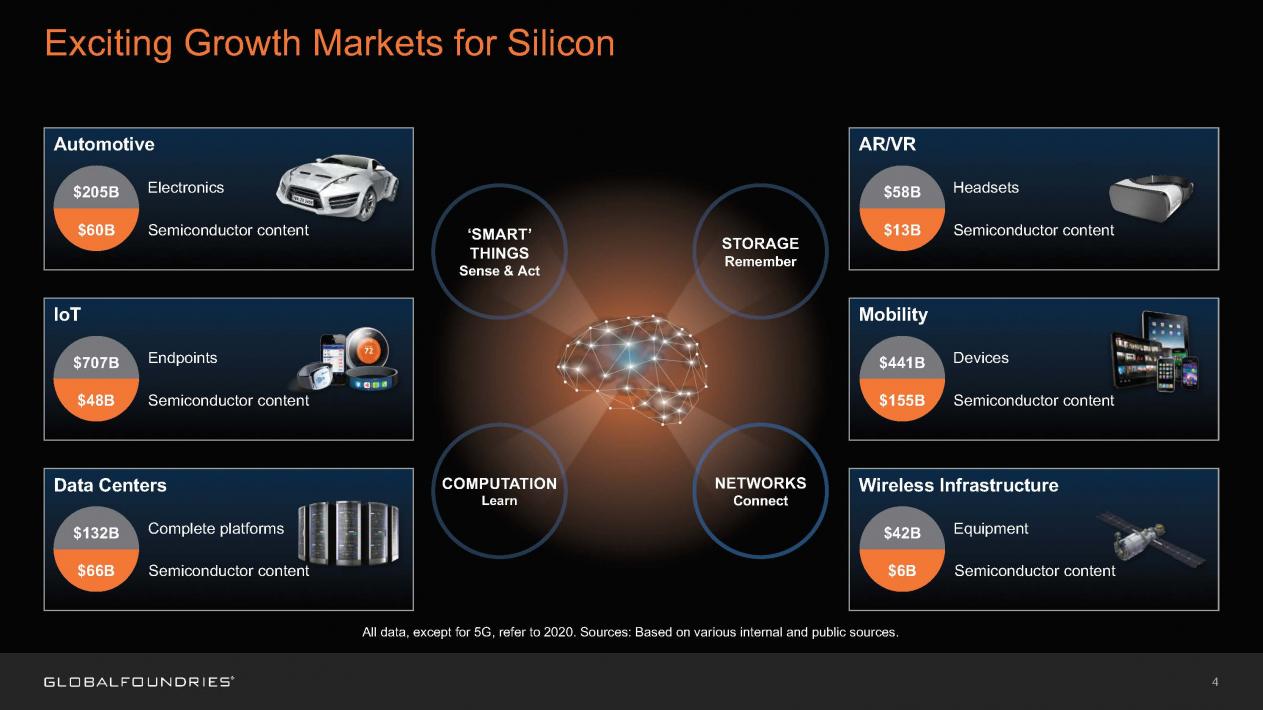

Imec Technology Forum: Gary Patton of GLOBALFOUNDRIES

The imec technology forum was held in Belgium last week. At the forum I had a chance to sit down with Gary Patton the CTO of GLOBALFOUNDRIES (GF) for an interview and he also presented “Enabling Connected Intelligence – Technology innovation: Enablers for an intelligent future” at the forum. In this article … Read More

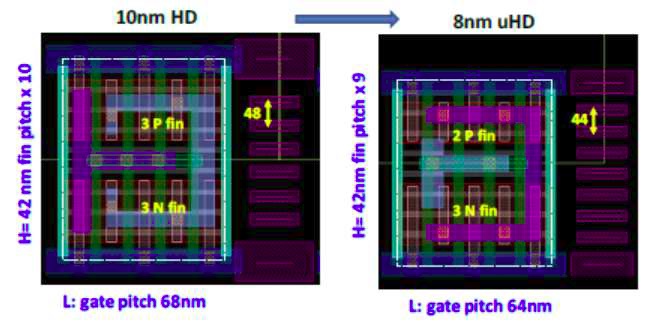

Samsung 10nm 8nm and 7nm at VLSIT

I got a tip sheet today for the upcoming 2018 Symposia on VLSI Technology & Circuits to be held June 19th through 21st in Honolulu, Hawaii. There is some interesting information on Samsung’s 10nm, 8nm and 7nm processes in the tip sheet:… Read More

Intel 10nm Yield Issues

On their first quarter earnings call Intel announced that volume production of 10nm has been moved from the second half of 2018 to 2019 due to yield issues. Specifically, they are shipping 10nm in low volume now, but yield improvement has been slower than anticipated. They report that they understand the yield issues but that improvements… Read More