You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Altera have been making use of Synopsys’s virtual platform technology to accelerate the time to volume by letting software development proceed in parallel with semiconductor development so that the software development does not need to wait until availability of hardware.

In the past, creating the virtual platform … Read More

In a discussion with one of my PR network recently, I found myself thinking out loud that if the merchant SoC market is getting squeezed hard, that validates something I’ve been thinking – the merchant CPU board market is dying from the middle out.… Read More

Aldec-Altera DO-254by Daniel Nenni on 09-25-2012 at 9:58 pmCategories: Aldec, EDA, FPGA

As described in DO-254, any inability to verify specific requirements by test on the device itself must be justified, and alternative means must be provided. Certification authorities favor verification by test for formal verification credits because of the simple fact that hardware flies not simulation models. Requirements… Read More

A Brief History of FPGAsby Daniel Nenni on 08-26-2012 at 7:30 pmCategories: FPGA

From the transistor to the integrated circuit to the ASIC, next comes programmable logic devices on the road to the mainstream fabless semiconductor industry. PLDS started in the early 1970’s from the likes of Motorola, Texas Instruments, and IBM but it wasn’t until Xilinx brought us the field programmable gate array (FPGA)… Read More

All semiconductor companies were caught up in ASIC in some way or another because of the basic economics. Semiconductor technology allowed medium sized designs to be done, and medium sized designs were pretty much all different. The technology didn’t yet allow whole systems to be put on a single chip. So semiconductor companies… Read More

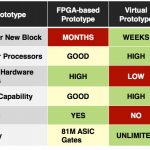

There are two main approaches to building a substructure on which to do software development and architectural analysis before a chip is ready: virtual platforms and FPGA prototyping.

Virtual platforms have the advantage that they are fairly quick to produce and can be created a long time before RTL design for the various blocks… Read More

AMS Programmable Prototype Platformsby ahmed.shahein on 05-21-2012 at 10:25 amCategories: Aldec, EDA, FPGA

AVNET released their 15[SUP]th[/SUP] Xfest this year, a couple of months ago. It was here in Germany last week. It was a well organized event, rich with invaluable technical information and full of decent smart engineers and managers. If you missed it this year register for the next event as soon as you can.

It was a very successful… Read More

EDPS: SoC FPGAsby Paul McLellan on 04-09-2012 at 4:00 amCategories: Events, FPGA

Mike Hutton of Altera spends most of his time thinking about a couple of process generations out. So a lot of what he worries about is not so much the fine-grained architecture of what they put on silicon, but rather how the user is going to get their system implemented. 2014 is predicted to be the year in which over half of all FPGAs will… Read More

New embedded computing standards always take a while to get traction, and a burning question for innovators is what to do in the period between concept and acceptance. Sometimes, new ideas come when commercial silicon changes direction.… Read More

SemiWiki would like to call you, your co-workers, and your company to participate at ERSA Conference in Las Vegas , July 16-19, 2012. I will be there and it would be a pleasure to work with you on this very important event!

ERSA, is Engineering of Reconfigurable Systems and Algorithms. Since this year, the emphasis will be on the commercial… Read More