The “old saw” is “To Sell in May and Go Away.” It’s a Maxim that particularly applies to semiconductor stocks as they typically drop from a post April earnings peak through the summer doldrums to a late September nadir only to be revived in the prelude of October earnings. It has happened again this year, although the path taken by the… Read More

Tag: fpga

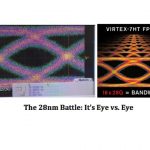

Altera and Xilinx Eyeing 28nm FPGA Dominance

28nm FPGAs are finally hitting the market and the next round in the battle between Altera and Xilinx is heating up. At 40nm, Altera beat Xilinx out the door by a year and as a consequence won a lot of new sockets in the high end Communications market. In the past year, Altera has closed the revenue and market share gap with Xilinx. This … Read More

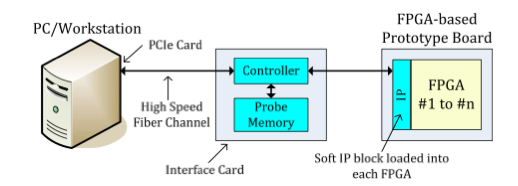

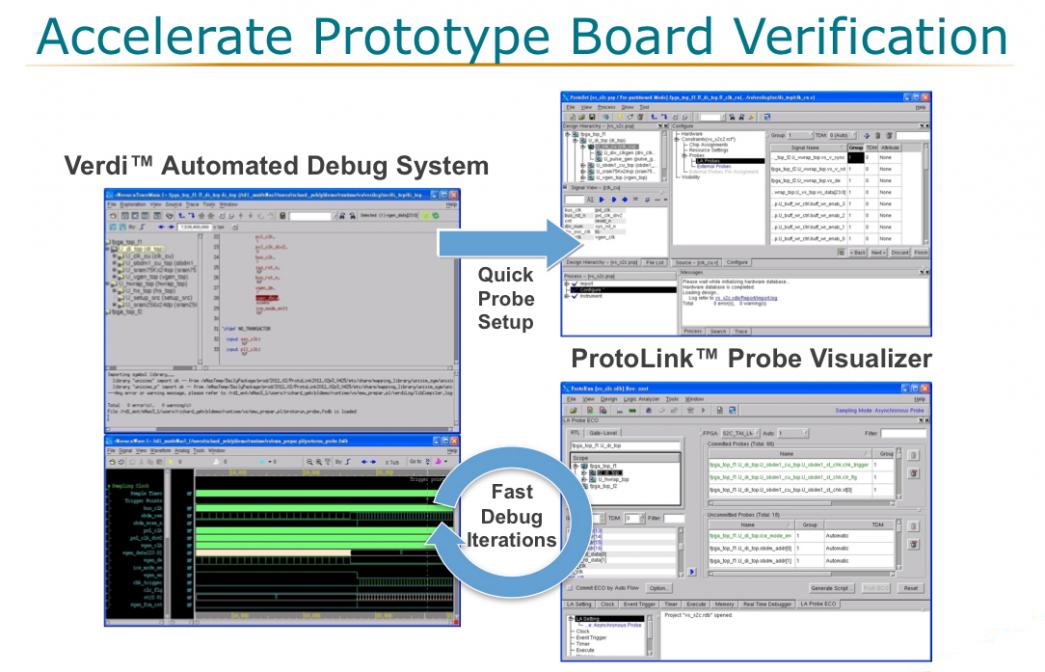

Speeding Verification of FPGA Prototype Boards

It is no secret that SoC designs continue to increase in complexity and time-to-market windows are shrinking. While there is room for debate on just how big a fraction of SoC design effort goes on verification, there is no debating that it is a large part of the total. Simulation is increasingly too slow, especially when software … Read More

FPGA Prototypes Made Easy

FPGA-based prototype boards are a fast, cost-effective platform for SoC system validation but they are notoriously difficult to set up and to debug. There is a big upside, however, allowing early software integration and testing and thus finding bugs in both the software and the SoC earlier. This approach is much cheaper than … Read More

Ivo Bolsens of Xilinx and Crossover Designs

I was at Mentor’s u2u (user group) meeting and one of the keynotes was by Ivo Bolsens of Xilinx. The other was by Wally Rhines and is summarized here.

Ivo started off talking analogizing SoCs as the sports-cars of the industry (fast but expensive), and FPGAs as the station wagons (not cool). In fact he even said that when Xilinx… Read More

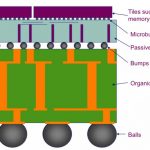

The World’s Smallest Printed Circuit Boards: interposers

Have you ever had the experience where you look up some unusual word in the dictionary since you don’t remember seeing it before. And then, in the next few weeks you keep coming across it. Twice in the last week I have been in presentations about the economics of putting die onto silicon interposers and the possibility of a new… Read More

Intel Buys an ARMy. Maybe

Is Intel in trouble? Since it is the #1 semiconductor company and, shipping 22nm in Q4 this year with 14nm in 2013, it is two process generations ahead of everyone else it is hard to see why it would be. Intel, of course, continues to dominate the market for chips for notebooks, desktops and servers. But therein lies the problem. Pads… Read More

Wanted: FPGA start-up! …Dead or Alive?

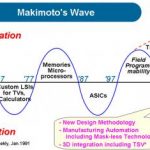

The recent announcement from Tabula about the $108 million raised in its Series D round of funding is putting the focus on FPGA technology, and FPGA startups in particular. Who are these FPGA startups, what is their differentiation, where is the innovation, in the product or the business model?

When you say FPGA, you first think:… Read More

TSMC Open Innovation Platform Explained

Launched in April 2008, the TSMC Open Innovation Platform initiative is a collaborative strategy aimed at breaking the bottlenecks of semiconductor design enablement in order to promote growth for the industry as a whole. The TSMC iPDK Debate: Lets Play Monopoly! blog I did provides more technical detail.

While Wafer count is… Read More