If you live in California anyway, with its large Asian population, you can’t have helped noticing that it was the Lunar New Year a couple of weeks ago, the start of the year of the sheep. A couple of days after the New Year, Xilinx announced their new families of what they now call FPGAs, 3D ICs and MPSoCs. But which the rest of us … Read More

Tag: fpga

Synflow and Cx

When hardware designers hear about a new language their heart sinks. We already have Verilog, SystemVerilog and VHDL. And if you go up a level, we have C, C++ and SystemC. Isn’t that enough? However, if you tell a software engineer about a new language they are interested, there are hundreds of programming language and hundreds… Read More

Got FPGA Timing Closure Problems?

I had a meeting with Harn Hua Ng, the CEO of Plunify, a couple of weeks ago. They are an EDA company that I’d never heard of. Partially that is because they only play in the FPGA space, a country I visit less frequently than SoC land. Plus, they are based in Singapore, a country I have only been to a couple of times in my life.

Plunify… Read More

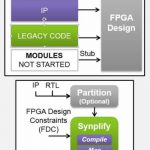

Dealing with FPGA IP in all its forms

One of the recurring themes I see here in the pages of SemiWiki and elsewhere is this pitched, bordering on religious battle between Altera and Xilinx. Just because both are FPGA technologies, the tendency is to put them in the same bucket, drawing direct comparisons between them. Some folks say there is no comparison; Xilinx has… Read More

Tabula Closes its Doors

I heard a rumor at lunchtime that Tabula was closing its doors. A friend of mine talked to a couple of employees and it is true. They have to be given 2 months notice apparently so the doors don’t actually close until March 24th. I thought they had raised $150M but Wikipedia (not always reliable of course) says $215M. They were … Read More

Altera Back to TSMC at 10nm? Xilinx Staying There

Xilinx announced their quarterly results last week. They slightly missed their number due mainly to a decline in wireless sales. Of course Xilinx parts don’t go in the smartphones since the cost and power are too high, but they are very heavily used in basestation, backhaul etc especially in China. Xilinx’s business… Read More

Xilinx ships the VU440 and its 4M logic cells

Xilinx has delivered not only “the biggest FPGA on the planet”, but what it claims is currently the world’s largest integrated circuit: the Virtex UltraScale VU440, with 19 billion transistors fabbed in TSMC 20nm. The list of first customers to receive parts says a lot about the state of SoC design today, and the vital role FPGA-based… Read More

New Vivado Release. And a Competition!

It is not entirely clear what Xilinx is these days. Of course it is an FPGA company. If you hear the word FPGA then I bet Xilinx is the first thing you think of. But what Xilinx ships these days is a far cry from the type of device it created when it was starting, where FPGAs were largely used to vacuum up all the glue logic around the processors… Read More

Is Your FPGA Design Secure? Use Xilinx to Make Sure

I hope your Christmas break is starting off well! You know this, but evil takes no break for Christmas. We are seeing more and more the hacking of systems and it seems to have become the norm. Do you get nervous anymore when you hear that your credit card company lost their data? Or I mean your data?

It’s as if we have given up on the ideas … Read More

Synthesizing rad-tolerant RTL for FPGAs

The maiden voyage of NASA’s Orion spacecraft brought a raft of articles about how the flight computer inside is “no smarter than your phone,” running on wheezing IBM PowerPC 750FX processors. NASA’s deputy manager for Orion avionics, Matt Lemke, admits the configuration is already obsolete – at least in commercial terms. … Read More