You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Ok, first thing first, Happy Thanksgiving! For the Miller’s as I get older, it is new traditions as some old ones have passed on. Memories are great and new ones to make. So you know the great debate right?

These poor people working Thanksgiving to sell some tablet or smart phone to save a few bucks. Those that must work, my condolences… Read More

For about a decade I am looking forward to seeing more of system level design and verification including high level synthesis (HLS), virtual prototyping, and system modeling etc. to come in the main stream of SoC design. Although the progress has been slow, I see it accelerating as more and more tools address the typical pain points… Read More

Xilinx announced their quarterly results a couple of days ago. Technically it is their Q2 2015. Sales were $604M and profitability was significantly higher than expected at $0.62/share. But that is not the most interesting thing about these calls. There is the Xilinx vs Altera story. And then there are tealeaves to be read about… Read More

When you think of Xilinx the word FPGA is the first that comes to mind. But Xilinx has really moved beyond the sort of simple glue-logic arrays that their first success was built on. A modern array contains processors as well as programmable fabric, hence the Xilinx tag-line “all programmable”. But another area that… Read More

Security of embedded devices is becoming more and more important. The requirement for good protection increases as devices become more interconnected: wearable medical devices that connect to the cloud, mobile base stations that are no longer up poles but in much less physically secure areas, cars that communicate among themselves.… Read More

ARM ♥ Xilinx!by Daniel Nenni on 09-28-2014 at 7:00 amCategories: Arm, FPGA, IP, Xilinx

The good news is that as a part of SemiWiki we get free media passes to all of the cool conferences. The bad news is that our inboxes get flooded with announcements. ARM TechCon is next week and my delete button is on overtime but it is interesting to see who is active in conferences and who is not. In this case Xilinx is very active and Altera… Read More

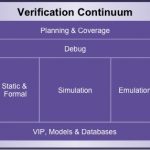

Verification spans a number of different technologies, from virtual platforms, RTL simulation, formal techniques, emulation and FPGA prototyping. Going back a few years, most of these technologies came from separate companies and one effect of this was that moving the design from one verification environment to another required… Read More

FPGA devices are a great way to drive silicon technology development because they contain both digital and analog IP, along with sophisticated IO cells. The highest performance IOs are transceivers, and Altera has recently designed the Arria 10 device family to include up to 96 transceivers, using a 20nm technology that can achieve… Read More

The growing capabilities of silicon along with improved algorithms means that machine vision is becoming increasingly important since more and more systems can be built in such areas as manufacturing, intelligent traffic management, bar code scanning, counterfeit detection and even sports simulation. Is that a 3X driver?… Read More

Xilinx announced their results today and had their conference call this afternoon, which I listened to. For them this is 1Q fiscal 2015 which means you have to be careful since there is a big difference between talking about fiscal quarters and calendar quarters. Xilinx’s conference calls are interesting for a couple of … Read More