As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

Tag: esd

Noise & Reliability of FinFET Designs – Success Stories!

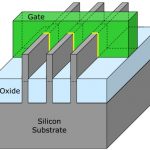

I think by now there has been good level of discussion on FinFET technology at sub-20 nm process nodes and this is an answer to ultra dense, high performance, low power, and billion+ gate SoC designs within the same area. However, it comes with some of the key challenges with respect to power, noise and reliability of the design. A FinFET… Read More

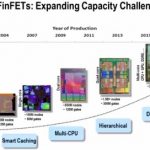

ANSYS Tools Shine at FinFET Nodes!

In the modern semiconductor ecosystem we are seeing rapid advancement in technology breaking past once perceived limits; 28nm, 20nm, 16-14nm, 10nm and we are foreseeing 7nm now. Double and multi-patterning are already being seen along with complex FinFET structures in transistors to gain the ultimate advantages in PPA from… Read More

Know All About ESD and Save Your Chips & Systems

In this age of electronics, especially with so many different types of human held devices and more upcoming wearable devices, it’s utmost important to protect the massive circuitry inside those tiny parts in the devices from ESD related failures. The protection needs to happen at all stages – cells inside the chips, package… Read More

The Carrington Event

Back in the pre-SemiWiki days when I had the EdaGrafitti blog I wrote about the Carrington event. This was a solar storm in 1859 that lasted for several days. On September 1st there was a coronal mass ejection (CME) traveling directly towards earth. Normally such an event would take several days to reach earth but an earlier ejection… Read More

Intel & Ansys Enable 14nm Chip Production

In the semiconductor industry, it feels great to hear about the process technology shrinking to lower nodes along with innovative transistor structures that offer major gains in PPA (Power, Performance and Area). However, it requires huge investment of capital, time and effort from foundries to conceptualize, prototype and… Read More

FinFET Based Designs Made Easy & Reliable

Although semiconductor manufacturing has taken off with FinFET based process technology which provides lucrative payoffs on performance improvement, power reduction and area saving in devices for high density and high performance SoC demand of modern era, apprehensions remain about its reliability due to reduced noise … Read More

EDA for Power Management ICs at DAC

I first met Dundar Dumlugolat Barcelona Design back in 2004, so it was a pleasure to meet with him again at DAClast week and learn more about what his company Magwel has to offer IC designers of power management chips.… Read More

RedHawk Excels – Customers Endorse

Since a few years, I have been following up Ansys Apachetools for semiconductor design, verification and sign-off. RedHawk is the most prominent platform of tools from Ansys, specifically for Power, Noise and Reliability Sign-off. It has witnessed many open endorsements from several of Ansyscustomers through open presentations,… Read More

ESD at TSMC: IP Providers Will Need to Use Mentor to Check

I met with Tom Quan of TSMC and Michael Beuler-Garcia of Mentor last week. Weirdly, Mentor’s newish buildings are the old Avant! buildings where I worked for a few weeks after selling Compass Design Automation to them. Odd sort of déja vu. Historically, TSMC has operated with EDA companies in a fairly structured way: TSMC … Read More