In the modern semiconductor ecosystem we are seeing rapid advancement in technology breaking past once perceived limits; 28nm, 20nm, 16-14nm, 10nm and we are foreseeing 7nm now. Double and multi-patterning are already being seen along with complex FinFET structures in transistors to gain the ultimate advantages in PPA from… Read More

Tag: electromigration

Cadence Completes Power Signoff Solution with Voltus-Fi

You probably remember Cadence introduced Voltus towards the end of last year at their signoff summit. This was aimed at digital designers. Prior to that they had announced Tempus, their static timing analysis tool. More recently they announced Quantus QRC extraction. All of these tools that end in -us have been re-architected… Read More

Intel & Ansys Enable 14nm Chip Production

In the semiconductor industry, it feels great to hear about the process technology shrinking to lower nodes along with innovative transistor structures that offer major gains in PPA (Power, Performance and Area). However, it requires huge investment of capital, time and effort from foundries to conceptualize, prototype and… Read More

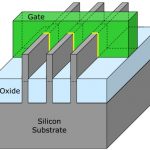

FinFET Based Designs Made Easy & Reliable

Although semiconductor manufacturing has taken off with FinFET based process technology which provides lucrative payoffs on performance improvement, power reduction and area saving in devices for high density and high performance SoC demand of modern era, apprehensions remain about its reliability due to reduced noise … Read More

RedHawk Excels – Customers Endorse

Since a few years, I have been following up Ansys Apachetools for semiconductor design, verification and sign-off. RedHawk is the most prominent platform of tools from Ansys, specifically for Power, Noise and Reliability Sign-off. It has witnessed many open endorsements from several of Ansyscustomers through open presentations,… Read More

Mission Critical Role of Unmanned Systems – How to fulfill?

Do we ever imagine what kind of severe challenges mission critical unmanned systems in air, land and underwater face? They are limited in space and size; have to be light in weight, flexible in different types of operations and at the same time rugged enough to work in extreme climatic conditions. That’s not enough; amidst these … Read More

How to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

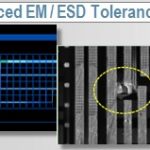

Reliability sign-off has several aspects – One Solution

Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

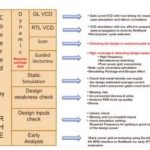

Electromigration (EM) with an Electrically-Aware IC Design Flow

Electromigration (EM) is a reliability concern for IC designers because a failure in the field could spell disaster as in lost human life or even bankruptcy for a consumer electronics company. In the old days of IC design we would follow a sequential and iterative design process of:… Read More

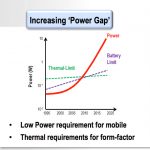

Power and Reliability Challenges

Last week I attended the Ansys/Apache seminars on “Dimensions of Electronic Design.” The two big challenges as we go down to 28nm and 20nm and below are keeping power manageable and keeping reliability up.

The big challenge with power is that we can put so much stuff on a die and clock it so fast that the power is exceeding… Read More