You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

A Brief History of RTDAby Paul McLellan on 10-05-2012 at 7:06 amCategories: EDA

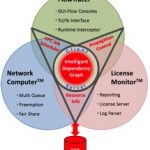

Andrea Casotto, the CEO of RTDA, started the company in Alameda in 1995, initially by himself, to market the FlowTracer software technology.

The early version of the technology was created as part of his PhD thesis at UC Berkeley, when Andrea sought automated ways to help engineering students who were having problems using EDA … Read More

While reading an article on DeepChip I found an interesting comment from Rafaela Novais, a Design Support Manager at TowerJazz Semi and decided to interview her to learn more about her experience as an IC designer and EDA tool user.

… Read More

EDA revenues for Q2 2012 were up 10.8% compared to Q2 2011 as reported by EDAC today.

Increasing

- CAE

- IC Physical Design & Verification

- Semi IP

…

Read More

IC designers of passive devices often use empirical approaches to perform High Frequency Analysis (HFA), however there is at least one new approach being offered by Mentor Graphics using a tool flow of:

…

Read More

ANSYS and Apache are putting on a new series of seminars about designing future electronic systems. These are only getting more complex, of course, cramming more and more functionality into smaller portable devices with good battery life (and not getting too hot), integrating multiple antennas into a single platform, and TSV-based… Read More

John Cooley has an interesting “scoop” on the Synopsys-EVE acquisition. The acquisition itself is not a surprise, it is the one big hole in Synopsys’s product line and EVE is the perfect plug to fill it. It was also about the only thing Cadence has (apart from PCB) that Synopsys does not.

The interesting thing … Read More

Converge in Detroitby Paul McLellan on 09-30-2012 at 10:04 pmCategories: EDA, Synopsys

When I worked for VaST we went to a show that I’d never heard of in EDA: SAE Convergence (SAE is the Society of Automotive Engineers). It is held once every two years and it focuses on transportation electronics, primarily automotive although there did seem to be some aerospace stuff there too. This is an even year, Convergence… Read More

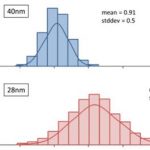

At DAC 2012 GLOBALFOUNDRIES and Solido presented a user track poster titled “Understanding and Designing for Variation in GLOBALFOUNDRIES 28-nm Technology” (as was previously announced here). This post describes the work that we presented.

We set out to better understand the effects of variation on design at 28-nm. In particular,… Read More

We’re plagued by acronyms in this business. Wikipedia defines RTL as follows: “In digital circuit design, register-transfer level (RTL) is a design abstraction which models a synchronous digital circuit in terms of the flow of digital signals (data) between hardware registers, and the logical operations performed on those… Read More

Aldec-Altera DO-254by Daniel Nenni on 09-25-2012 at 9:58 pmCategories: Aldec, EDA, FPGA

As described in DO-254, any inability to verify specific requirements by test on the device itself must be justified, and alternative means must be provided. Certification authorities favor verification by test for formal verification credits because of the simple fact that hardware flies not simulation models. Requirements… Read More