At DAC 2012 GLOBALFOUNDRIES and Solido presented a user track poster titled “Understanding and Designing for Variation in GLOBALFOUNDRIES 28-nm Technology” (as was previously announced here). This post describes the work that we presented.

We set out to better understand the effects of variation on design at 28-nm. In particular, we had the following questions:

- How does process variation compare between 28-nm and 40-nm?

- How do process corners compare vs. statistical variation?

- How can variation be handled effectively in 28-nm custom design?

To answer these questions we looked at GLOBALFOUNDRIES 28-nm and 40-nm technologies, and performed variation-aware analysis and design with Solido Variation Designer.

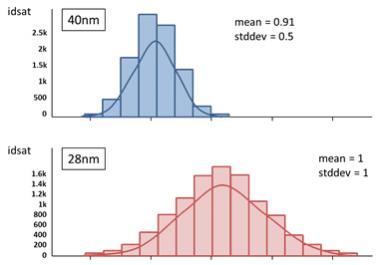

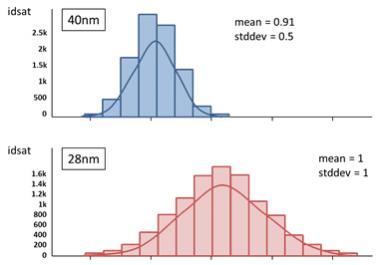

We first looked at how process variation has changed from GLOBALFOUNDRIES 40-nm technology to the 28-nm technology by measuring transistor saturation current, idsat, for a minimum-size transistor in each technology. The plots below show the statistical distribution of idsat in 28-nm (left) and 40-nm (right) technology with global variation applied. The results show a significant overall increase in idsat variation from 40-nm to 28-nm. When both global variation and mismatch effects were included, the overall increase in idsat variation was lower, but still quite significant. This result underscores the increasing importance of accounting for variation.

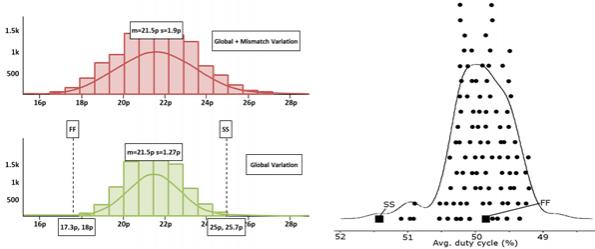

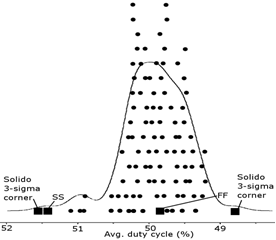

Next we used a delay cell and a PLL VCO design to compare PVT corner simulations with statistical simulations in GLOBALFOUNDRIES 28-nm technology. The plots below show the the results for the delay cell (left) and for the PLL VCO (right). From the plots it can be seen that, for the simple delay cell, the FF and SS process corners reasonably predict the tail region of the statistical performance distribution. However, for the more complex PLL VCO, the FF and SS corners do not align well with the best- and worst-case performance of the statistical distribution. This is because simple FF and SS corners are normally extracted based on digital performance assumptions and often do not reflect the true worst-case performance conditions of a particular design. To avoid this fundamental limitation, it is necessary either to increase the number of corners being simulated or else to use statistical simulation.

Solido Variation Designer helps with both of these approaches: Solido’s fast PVT analysis can be used when a large number of corners exist to reduce the number of simulations required, and Solido’s sigma-driven corner extraction capability can find accurate statistical corners that can be used instead of the traditional process corners.

Variation-Aware Design with the 28-nm PLL VCO

With the PLL VCO design, we used Solido Variation Designer to perform both fast PVT corner analysis and statistical design (3-sigma and high-sigma analysis).

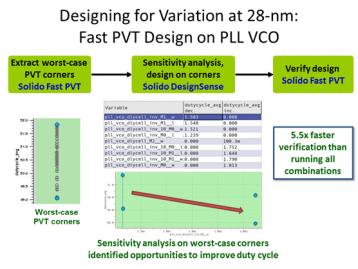

PVT corner analysis is an integral part of a variation-aware design flow, taking into account different process conditions for various devices (e.g. mos, resistor, capacitor, etc.) as well as environmental conditions that may affect the design (e.g. voltage, temperature, bias, load). When designing for 28-nm technology, the number of corner combinations can readily become very large.

For the PLL VCO design, the conditions that needed to be taken into account were: process conditions for mos, resistor, and capacitor; along with voltage and temperature conditions. Even with just these few conditions, several hundred combinations needed to be considered to properly provide coverage for the design. Since the PLL VCO has a relatively long simulation time to measure its duty cycle, it would be very time consuming to simulate all combinations to provide sufficient coverage of the design.

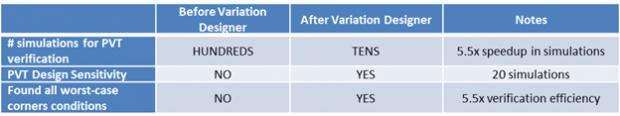

The steps we used for fast PVT design with Solido Variation Designer are shown below:

Solido Variation Designer’s Run Fast PVT application made it possible to find the worst-case conditions 5.5x faster than running all combinations. Furthermore, the results from Fast PVT could then be used with Solido’s DesignSense application to determine the sensitivity of the design under variation-aware conditions. This made it much more practical to perform iterative design, and to explore opportunities to improve the duty cycle performance under worst-case conditions.

Statistical variation analysis and design is another key part of variation-aware design. As discussed earlier, corner analysis does not always capture design performance properly under variation conditions. Furthermore, specific sigma levels often need to be achieved, such as 6-sigma, which require the use of statistical simulation.

Solido Variation Designer makes it possible to verify designs at any practical sigma level. For lower-sigma designs, such as 3-sigma, Solido Variation Designer can be used with GLOBALFOUNDRIES models to extract 3-sigma corners, perform design iteration, and verify the design. The image below shows the result of performing 3-sigma corner extraction on the PLL VCO duty cycle. As can be seen in the image, Variation Designer was able to extract corners for the PLL VCO design that bound the distribution much better than the FF/SS corners.

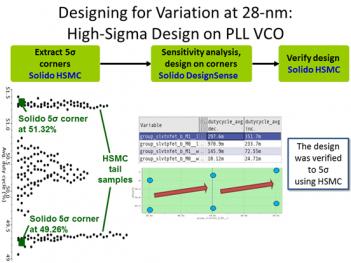

For higher sigma levels, using Solido Variation Designer’s High-Sigma Monte Carlo (HSMC) capability makes it possible to perform fast, accurate, scalable and verifiable high-sigma design. This is important for high-volume and/or high-quality designs including memory, standard cell, automotive, and medical applications.

The steps we used for high-sigma design with Solido Variation Designer are shown below:

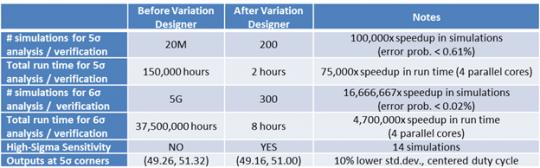

Solido Variation Designer provided a 100,000x and 16,666,667x reduction in the number of simulations required to accurately verify the design to 5- and 6-sigma, respectively. In addition, Variation Designer allowed the extraction of precise high-sigma corners that could be used to design iteratively while taking into account high-sigma variation.

Below are the results from statistical design with the PLL VCO:

It was clear during our work that variation is an important consideration for design at 28-nm. To achieve yielding, high-performance designs, it is necessary to be aware of variation and take it into account in the design flow. Using Solido Variation Designer with GLOBALFOUNDRIES technology makes it possible to do this efficiently and accurately.

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!