This certainly was an interesting year. The fabless semiconductor ecosystem definitely got stronger and I see nothing but clear skies in 2014. Judging by the SemiWiki 2013 analytics and key search terms we all have an interesting year ahead of us with even more opportunities to grow and innovate. 2013 was also a year of growth and… Read More

Tag: eda

2013 Awards, and the Winner is…Power

Of all the things that designers have to worry about in the power-performance-area (PPA) equation, the most challenging is power. SoCs have reached a point that we can put a lot of stuff on them, but if we are not careful we cannot light it all up at once. Dark silicon, where we put subsystems on a chip but then don’t have enough … Read More

ClioSoft at Arasan

Arasan recently adopted ClioSoft for data management (DM) for design and development of Arasan’s Silicon IP products. This morning I talked to Erik Peterson, Senior CAD and Verification Engineer AMS Design about their experiences bringing up ClioSoft.

Data management infrastructure is critical with engineering projects… Read More

Highest Test Quality in Shortest Time – It’s Possible!

Traditionally ATPG (Automatic Test Pattern Generation) and BIST (Built-In-Self-Test) are the two approaches for testing the whole semiconductor design squeezed on an IC; ATPG requires external test equipment and test vectors to test targeted faults, BIST circuit is implemented on chip along with the functional logic of IC.… Read More

Social Media at Silvaco

Founded back in 1984, Silvaco has been in business for some 29 years now, focusing on the TCAD and EDA markets.

Browsing their Home page at www.silvaco.com we find four social media links in the footer: Facebook, Twitter, YouTube and LinkedIn.… Read More

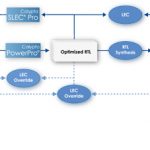

SLEC is Not LEC

One of the questions that Calypto is asked all the time is what is the difference between sequential logical equivalence checking (SLEC) and logical equivalence checking (LEC).

LEC is the type of equivalence checking that has been around for 20 years, although like all EDA technologies gradually getting more powerful. LEC is … Read More

Happy Holidays from Atrenta

It is that time of year and once again Atrenta has produced a video wishing you all the best for the holiday season. They are so spread around the world it is not just Hanukkah and Christmas but the Asian Lunar New Year (end of January) and probably some more holidays I don’t even know about. Last year there was a competition to name… Read More

Security Path Verification

Formal approaches and security are a perfect match since you really want to prove that there are no holes in your security, rather than just being fairly confident. At the recent Jasper User Group meeting, Victor Purri presented some case studies in security verification.

The Jasper Security Path Verification (SPV) App is used… Read More

Mentor Buys Oasys

Mentor is acquiring Oasys, subject to all the usual caveats about shareholder and regulatory approval. The shareholder paperwork went out earlier this week. The common stock is valueless so presumably the price is low (and Mentor historically has not paid high prices for its acquisitions).

So what is going to happen with the technology?… Read More

Known Unknowns and Unknown Unknowns

Donald Rumsfeld categorized what we knew into known unknowns and unknown unknowns. In a chip design, those unknown unknowns can bite you and leave you with a non-functional design, perhaps even intermittent failures which can be among the hardest problems to debug.

Chips are too big to do any sort of full gate-level simulation,… Read More