It was back in 1991 that Cadence first announced the Virtuoso product name, and here we are 32 years later and the product is alive and doing quite well. Steven Lewis from Cadence gave me an update on something new that they call Virtuoso Studio, and it’s all about custom IC design for the real world. In those 32 years we’ve… Read More

Tag: custom design

FinFET Custom Design

At CDNLive, Bob Mullen of TSMC gave a presentation on their new custom FinFET flow, doing design, and verifying designs. At 16nm there are all sorts of relatively new verification problems such as layout dependent effects (LDE) and voltage dependent design rules. We had some of this at 20nm but like most things in semiconductor,… Read More

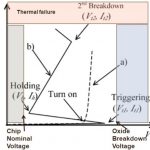

Full Chip ESD Sign-off – Necessary

As Moore’s law keeps going, semiconductor design density on a chip keeps increasing. The real concern today is that the shrinkage in technology node has rendered the small wire geometry and gate oxide thickness (although fine in all other perspectives) extremely vulnerable to ESD (Electrostatic Discharge) effects. More than… Read More

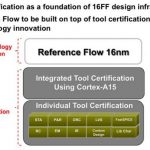

TSMC’s 16FinFET and 3D IC Reference Flows

Today TSMC announced three reference flows that they have been working on along with various EDA vendors (and ARM and perhaps other IP suppliers). The three new flows are:

- 16FinFET Digital Reference Flow. Obviously this has full support for non-planar FinFET transistors including extraction, quantized pitch placement, low-vdd