Clock domain crossing (CDC) analysis has been around for many years, initially as special checks in verification or static timing analysis, but it fairly quickly diverged into specialized tools focused just on this problem. CDC checks are important because (a) you can lose data or even lock up at, or downstream of a poorly-handled… Read More

Tag: cdc

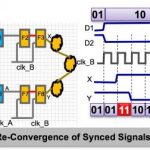

Syncing Up CDC Signals in Low Power Designs

So far in my blog series on low power we’ve looked broadly at what’s changing in the low power verification landscape and focused on a new methodology developed by Mentor Graphics and ARM called successive refinement, which is now included in the UPF standard. Power management techniques create their own brand of clock domain crossing… Read More

New Vivado release goes from Lab to UltraScale

Xilinx users will welcome the brand-new release of Vivado Design Suite 2015.1. For openers, device support for the latest FPGAs in the UltraScale family – XCVU440, XCVU190, and XCVU125 – has been added in the release, and early access code for the XCVU160 is available from a local Xilinx FAE. Installation has been streamlined, … Read More

A Comprehensive Power Optimization Solution

In an electronic world driven by smaller devices packed with larger functions, power becomes a critical factor to manage. With power consumption leading to heat dissipation issues, reliability of the device can be affected, if not controlled or the device not cooled. Moreover, for mobile devices such as smartphones or tablets… Read More

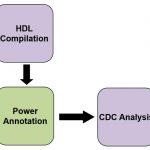

CDC Verification: A Must for IP and SoCs

In the modern SoC era, verification is no longer a post-design activity. The verification strategy must be planned much earlier in the design cycle; otherwise the verification closure can become a never ending problem. Moreover, verification which appears to be complete may actually be incomplete because of undetected issues… Read More

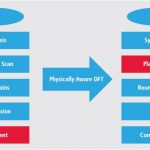

Physically Aware DFT Improves PPA

Introducing on-chip test circuitry has become a necessary criteria for an ASIC’s post manufacture testability. The test circuitry is usually referred as DFT (Design-for-Test) circuit. A typical methodology for introducing DFT circuit in a design is to replace usual flip-flops with special types of flip-flops called ‘scan… Read More

Writing the unwritten rules with ALINT-PRO-CDC

EDA verification tools generally do a great job of analyzing the written rules in digital design. Clock domain crossings (CDCs) are more like those unwritten rules in baseball; whether or not you have a problem remains indefinite until later, when retaliation can come swiftly out of nowhere.

Rarely as overt or dramatic as a bench-clearing… Read More

Expert Tool to Easily Debug RTL and Reuse in SoCs

SoC design these days has become a complex and tricky phenomenon involving integration of multiple IPs and legacy RTL code which could be in different languages, sourced from various third parties across the globe. Understanding and reusing RTL code is imperative in SoC integration which needs capable tools that can accommodate… Read More

A Complete Scalable Solution for IP Signoff

In an SoC world driven by IP, where an SoC can have hundreds of IP (sourced not only from 3[SUP]rd[/SUP] party but also from internal business units which can have a lot of legacy) integrated together, it has become essential to have a comprehensive and standard method to verify and signoff the IP. Additionally, these checks must … Read More

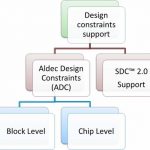

A Complete Timing Constraints Solution – Creation to Signoff

With the unprecedented increase in semiconductor design size and complexity design teams are required to accommodate multiple design constraints such as multiple power domains for low power design, multiple modes of operation, many clocks running, and third party IPs with different SDCs. As a result timing closure has become… Read More