Lu Dai (chair of Accellera) and I had our regular chat at DVCon U.S. 2026. Accellera also hosted a reception in the exhibits hall, with free snacks and drinks, very well attended. We talked about what’s new in Accellera, with a particular emphasis on the recently released standard for CDC and RDC tool interoperability, also Lu’s … Read More

Tag: cdc

Automating Reset Domain Crossing (RDC) Verification with Advanced Data Analytics

The complexity of System-on-Chip (SoC) designs continues to rise at an accelerated rate, with design complexity doubling approximately every two years. This increasing complexity makes verification a more difficult and time-consuming task for design engineers. Among the key verification challenges is managing reset domain… Read More

Handling metastability during Clock Domain Crossing (CDC)

SoC designs frequently have lots of different clock domains to help manage power more efficiently, however one side effect is that when the clock domains meet, i.e., in a Clock Domain Crossing (CDC), there’s the possibility of setup and hold time violations that can cause a flip-flop to become metastable. Synchronizer … Read More

DVCon Europe is Coming Soon. Sign Up Now

I’m a fan of DVCon, a fan of Accellera and a fan of Munich, hosting DVCon Europe once again. This year’s event runs from November 14th through 15th (with some events on the 16th) at the Holiday Inn Munich in the City Center. Phillippe Notton (CEO, SiPearl) will deliver a keynote on “Energy Efficient High-Performance Computing in the… Read More

Accellera and Clock Domain Crossing at #60DAC

Accellera sponsored a luncheon panel discussion at #60DAC, so I registered and attended to learn more about one of the newest working groups for Clock Domain Crossing (CDC). An overview of Accellera was provided by Lu Dai, then the panel discussion was moderated by Paul McLellan of Cadence, with the following panel members:

- Anupam

Getting to Faster Closure through AI/ML, DVCon Keynote

Manish Pandey, VP R&D and Fellow at Synopsys, gave the keynote this year. His thesis is that given the relentless growth of system complexity, now amplified by multi-chiplet systems, we must move the verification efficiency needle significantly. In this world we need more than incremental advances in performance. We need… Read More

CEO Interview: Sivakumar P R of Maven Silicon

Sivakumar P R is the Founder and CEO of Maven Silicon. He is responsible for the company’s vision, overall strategy, business, and technology. He is also the Founder and CEO of Aceic Design Technologies.

Sivakumar is a seasoned engineering professional who has worked in various fields, including electrical engineering,… Read More

CDC, Low Power Verification. Mentor and Cypress Perspective

Clock domain crossing (CDC) analysis is unavoidable in any modern SoC design and is challenging enough to verify in its own right. CDC plus low power management adds more excitement to your verification task. I wrote on this topic for another solution provider last year. This time I want to intro an interesting twist on the problem,… Read More

Structural CDC Analysis Signoff? Think Again.

Talking not so long ago to a friend from my Atrenta days, I learned that the great majority of design teams still run purely structural CDC analysis. You should sure asynchronous clock domains are suitably represented in the SDC, find all places where data crosses between those domains that require a synchronizer, gray-coded FIFO… Read More

What’s New in CDC Analysis?

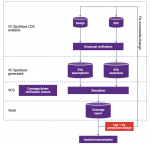

Synopsys just released a white paper, a backgrounder on CDC. You’ve read enough of what I’ve written on this topic that I don’t need to re-tread that path. However, this is tech so there’s always something new to talk about. This time I’ll cover a Synopsys survey update on numbers of clock domains in designs, also an update on ways to… Read More