You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I’m always curious to learn what might be new in clock domain crossing (CDC) verification, having dabbled in this area in my past. It’s an arcane but important field, the sort of thing that if missed can put you out of business, but otherwise only a limited number of people want to think about it to any depth.

The core issue is something… Read More

Bugs are an inescapable reality in any but the most trivial designs and usually trace back to very deterministic causes – a misunderstanding of the intended spec or an incompletely thought-through implementation of some feature, either way leading to reliably reproducible failure under the right circumstances. You run diagnostics,… Read More

When I was at Atrenta, we took advantage of opportunities to expand our static tool (aka linting) first to clock domain crossing (CDC) analysis and DFT compatibility and later to static analysis of timing constraints, all of which have importance in implementation. CDC is commonly thought of as an RTL-centric analysis, however,… Read More

RDC – A Cousin To CDCby Alex Tan on 04-18-2018 at 12:00 pmCategories: Aldec, EDA, FPGA

In a post-silicon bringup, it is customary to bring the design into a known state prior to applying further testing sequences. This is achieved through a Power-on-Reset (POR) or similar reset strategy which translates to initializing all the storage elements to a known state.

During design implementation, varying degrees of… Read More

Clock Domain Crossing (CDC) is a common occurrence in a multiple clock design. In the FPGA space, the number of interacting asynchronous clock domains has increased dramatically. It is normal to have not hundreds, but over a thousand clock domains interactions. Let’s assess why CDC is a lingering issue, what its impact and the … Read More

In the early days of IP reuse and platform-based design there was a widely-shared vision of in-house IP development teams churning out libraries of reusable IP, which could then be leveraged in many different SoC applications. This vision was enthusiastically pursued for a while; this is what drove reusability standards and … Read More

FPGAs have become a lot more capable and a lot more powerful, more closely resembling SoCs than the glue-logic we once considered them to be. Look at any big FPGA – a Xilinx Zynq, an Intel/Altera Arria or a Microsemi SmartFusion; these devices are full-blown SoCs, functionally different from an ASIC SoC only in that some of the device… Read More

If there’s anyone out there who still doesn’t accept the importance of static RTL verification in the arsenal of functional verification methods, I haven’t met any recently. That wasn’t the case in my early days in this field. Back then I grew used to hearing “I don’t make mistakes in my RTL”, “I’ll catch that in simulation”, “My editor… Read More

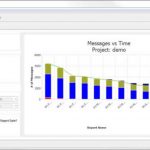

You’re an RTL pro. You know what’s inside your code, and how many bugs you’ve tracked down and exterminated along the development path, and how much work remains. So, why did the meeting notice that just popped up asking for a monthly management project review presentation ruin your day?… Read More

Our previous Blue Pearl post looked at the breadth of contextual visualization capability in the GUI to speed up debug. Two other important aspects of the ASIC & FPGA pre-synthesis workflow are automating analysis with scripts and managing the stream of messages produced. Let’s look at these aspects… Read More