Weebit Nano, a leading developer of advanced memory technologies, recently announced a significant collaboration with DB HiTek, one of the top ten foundries of the world. The collaboration is designed to enable integration of Weebit’s Resistive Random-Access Memory (ReRAM) into DB HiTek’s 130nm Bipolar-CMOS-DMOS… Read More

Tag: beol

BEOL Mask Reduction Using Spacer-Defined Vias and Cuts

In recent advanced nodes, via and cut patterning have constituted a larger and larger portion of the overall BEOL mask count. The advent of SALELE [1,2] caused mask count to increase for EUV as well, resulting in costs no longer being competitive with DUV down to 3nm [3]. Further development by TEL [4] has shown the possibility for… Read More

How an Embedded Non-Volatile Memory Can Be a Differentiator

Embedded memory makes computing applications run faster. In the early days of the semiconductor industry, the desire to utilize large amount of on-chip memory was limited by cost, manufacturing difficulties and technology mismatches between logic and memory circuit implementations. Since then, advancements in semiconductor… Read More

ReRAM Revisited

I met with Sylvain Dubois (VP BizDev and Marketing of Crossbar) at TechCon to get an update on his views on ReRAM technology. I’m really not a semiconductor process guy so I’m sure I’m slower than the experts to revelations in this area. But I do care about applications so I hope I can add an app spin on the topic, also Sylvain’s views on… Read More

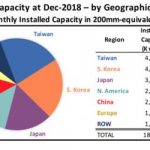

Physical Design for Secure Split Manufacturing of ICs

Semiconductors are not only critical to modern life, semiconductors are critical to National Security. Now that leading edge semiconductor foundries have left the United States one of the more pressing challenges is secure semiconductor manufacturing. This applies to all countries of course so let’s take a look at the International… Read More

Where Circuit Simulation Model Files Come From

I started out my engineering career by doing transistor-level circuit design and we used a proprietary SPICE circuit simulator. One thing that I quickly realized was that the accuracy of my circuit simulations depended entirely on the model files and parasitics. Here we are 40 years later and the accuracy of SPICE circuit simulations… Read More

SPICE Model Generation by Machine Learning

It was 1988 when I got into SPICE (Simulation Program with Integrated Circuit Emphasis)while I was characterizing a 1.5 μm Standard cell library developed by students at my Alma-Mata Furtwangen University in Germany. My professor Dr. Nielinger was not only my advisor he also wrote the first SPICE bible in German language. At that… Read More

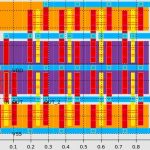

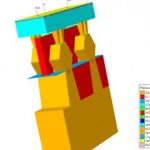

SEMICON West – Advanced Interconnect Challenges

At SEMICON West I attended the imec technology forum where Zsolt Tokei presented “How to Solve the BEOL RC Dilemma” and the SEMICON Economics of Density Scaling session where Larry Clevenger of IBM presented “Interconnect Scaling Strategic for Advanced Semiconductor Nodes”. I also had the opportunity… Read More

IMEC Technology Forum (ITF) – EUV When, Not If

For me personally EUV has been something of a roller coaster ride over the last several years. I started out a strong believer in EUV but then at the SPIE Advanced Lithography Conference in 2014 TSMC gave a very negative assessment of EUV, and there was a SEMATECH paper on high NA EUV that struck me as extremely unlikely to succeed. I … Read More

Samsung Versus Intel at 14nm

Daniel Nenni recently blogged about Intel’s claims of industry leading process density that were made at their analysts meeting. It isn’t clear to me why Intel makes this such a big focus at the analysts meetings, they really don’t compete with the foundries much but this seems to be a big deal to them. I thought it would be interesting… Read More