You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Design starts are the lifeblood of the semiconductor industry which is why we have been following the eSilicon STAR Platform since its introduction with great anticipation. The STAR platform was first launched about three years ago. Today, there are over 1,300 registered STAR users in 52 countries around the world.

The ASIC business… Read More

You’re an RTL pro. You know what’s inside your code, and how many bugs you’ve tracked down and exterminated along the development path, and how much work remains. So, why did the meeting notice that just popped up asking for a monthly management project review presentation ruin your day?… Read More

Aldec tools and services have long been associated with FPGA designs. As FPGAs have evolved toward more RTL-based designs, the similarities between a modern FPGA verification flow and an ASIC verification flow often leave them looking virtually the same. … Read More

In my initial look at ClioSoft’s design management system created from the ground up for the semiconductor industry, I made the opening case for managing and reusing IP across an ASIC design organization. Let’s for a moment say we agree on the need for an enterprise software package to do design management… Read More

We introduced the philosophy behind the Blue Pearl Software suite of tools for front-end analysis of ASIC & FPGA designs in a recent post. As we said in that discussion, effective automation helps find and remedy issues as each re-synthesis potentially turns up new defects. Why do Blue Pearl users say their tool suite is easier… Read More

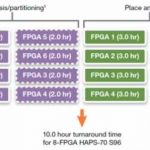

Speaking of having the right tools, FPGA-based prototyping has become as much if not more about the synthesis software than it is about the FPGA hardware. This is a follow-up to my post earlier this month on FPGA-based prototyping, but with a different perspective from another vendor. Instead of thinking about what else can be done… Read More

FPGA prototyping has come a long way since the late 1980s when chipmakers began using FPGA devices for building system prototypes of ASIC designs. The utility of a working FPGA prototype allows hardware designers to develop and test their systems, and it provides software developers early access to a fully functioning hardware… Read More

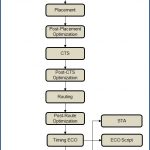

Today, in the design of any type of system on chip (SoC), timing closure is a major problem and it only gets worse with each new, and more advanced process technology. Timing closure is closely inter-leaved with power and clock design. The complexity of achieving closure rises sharply with increasing design density and advancing… Read More