This year’s #50DAC will be chock-full of technical content because that is what attracts the masses of semiconductor professionals, like moths to a flame, or like me to a Fry’s Electronics store. Interesting note, I went to high school with Randy Fry. His Dad started the Fry’s supermarket chain which he sold… Read More

Tag: aldec

Beyond one FPGA comfort zone

Unless you are a small company with one design team, the chance you have standardized on one FPGA vendor for all your needs, forever and ever, is unlikely. No doubt you probably have a favorite, because of the specific class of part you use most often or the tool you are most familiar with, but I’d bet you use more than one FPGA vendor routinely.… Read More

10 to 100X faster HDL Simulation Speeds

Speed, capacity, accuracy – these are the three major EDA tool metrics that we pay attention to and that enable us to design and verify an SoC. Talk to any design or verification engineer and ask if they are satisfied with the time that it takes to simulate their latest design, or to verify that it meets spec and is functionally… Read More

Webinar: Making a Simple, Structured and Efficient VHDL Testbench

Most simple testbenches have close to no structure, are terrible to modify and hopeless to understand. They often take far too much time to implement and provide close to no support when debugging potential problems. This webinar will demonstrate how to build a far better testbench with respect to all these issues – in significantly… Read More

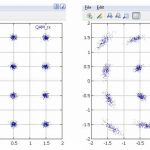

Plotting to take over the time-domain only world

The state machine nature of many digital designs has made time-domain debugging the favorite tool for most designers. We provide a set of inputs, data gets clocked in, and a set of outputs appears. We look for specific patterns in parallel paths, or sequences on serial lines.… Read More

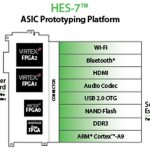

ARM Cortex SoC Prototyping Platform for Industrial Applications

If your next SoC uses an ARM Cortex-A9 and has an industrial application, then you can save much design and debug time by using a prototyping platform. The price to prototype is quite affordable, and the methodology has a short learning curve. Bill Tomasan Aldec Research Engineer conducted a webinar today on: ARM Cortex SoC Prototyping… Read More

Learning Properties, Assertions and Covers for Hardware Design

How do you learn new hardware design topics? I just got trained online about property-based verification for hardware designers using a free online class at Aldec. The material was created by Jerry Kaczynski, a Research Engineer at Aldec.

Aldec Delivers Leading Verification Methodologies!

For those of you who don’t know, Aldec Inc., headquartered in Henderson, Nevada, is an industry leader in Electronic Design Verification and offers a patented technology suite including: RTL Design, RTL Simulators, Hardware-Assisted Verification, ASIC Prototyping, Design Rule Checking, IP Cores, DO-254 Functional Verification… Read More

UVM: Lowering the barrier to IP reuse

One of my acquaintances at Intel must have some of the same viewing habits I do, based on a recent Tweet he sent. He was probably watching “The Men Who Built America” on the History Channel and thinking as I have a lot recently about how the captains of industry managed to drive ideas to monopolies in the late 1800s and early 1900s.

… Read MoreDifference

Zynq out of the box, in FPGA-based prototyping

Roaming around the hall at ARM TechCon 2012 left me with eight things of note, but one of the larger ideas showing up everywhere is the Xilinx Zynq. Designers are enthralled with the idea of a dual-core ARM Cortex-A9 closely coupled with programmable logic.… Read More